# MEMORY CUSTOMIZATION IN MULTIPROCESSOR SYSTEMS-ON-CHIP

#### A THESIS

Submitted in partial fulfillment of the requirements for the award of the degree of

### DOCTOR OF PHILOSOPHY

ΙN

COMPUTER SCIENCE & ENGINEERING

BY

### SHAILY MITTAL

(Enrollment No.: 106208)

Department of Computer Science & Engineering and Information Technology, Jaypee University of Information Technology, Waknaghat, Solan-173234, Himachal Pradesh, INDIA

APRIL 2014

# MEMORY CUSTOMIZATION IN MULTIPROCESSOR SYSTEMS-ON-CHIP

#### A THESIS

Submitted in partial fulfillment of the requirements for the award of the degree of

### DOCTOR OF PHILOSOPHY

ΙN

COMPUTER SCIENCE & ENGINEERING

BY

### SHAILY MITTAL

(Enrollment No.: 106208)

Department of Computer Science & Engineering and Information Technology, Jaypee University of Information Technology, Waknaghat, Solan-173234, Himachal Pradesh, INDIA

APRIL 2014

### **ACKNOWLEDGEMENTS**

I sincerely express my gratitude to my advisor, Dr. Nitin, for consistent guidance in this research work. I am fortunate to have blessings of almighty, brought closer to my advisor, is always interested in exploring new research directions and ideas with deep vision, encouragement and dimension. He gave freedom in performing research activities and ensured that my various contents are neatly tied together. He has personal touch and support to all his students. One can easily feel friend and philosopher in his disposition.

This research has benefited from the ideas and suggestions of many well wishers. Special thanks to Management, Jaypee Sewa Sansthan especially to Dr. Yajulu Medury, COO–Jaypee Education System & founder Vice Chancellor, Brig. Balbir Singh (Retd.), Director and Prof.(Brig.) S.P.Ghera, HOD CSE department, Jaypee University of Information Technology, Waknaghat, for providing excellent research environment and learning ambiance at the campus.

I am eternally grateful to my respected Mother, Father, Mother-in-law, Father-in-law and affectionate younger Brother and Sister-in law beyond words and for the most devoted and supportive Husband for his love and support he have given me all over these years. Without their sustained moral support, it would have been impossible to succeed in writing this wonderful thesis.

Shaily Mittal

### CANDIDATE'S DECLARATION

I hereby certify that the work, which is being presented here in the thesis entitled, MEMORY CUSTOMIZATION IN MULTIPROCESSOR SYSTEMS-ON-CHIP, submitted in partial fulfillment of the requirements for the award of the degree of Doctor of Philosophy in Computer Science & Engineering and submitted in Department of Computer Science & Engineering and Information Technology, Jaypee University of Technology (JUIT), Solan is an authentic record of my own work carried out (July 2010–April 2014) under the supervision and guidance of Dr. Nitin, Associate Professor, Department of Computer Science & Engineering and Information Technology Chancellor, JUIT, Solan.

I hereby declare that this Doctor of Philosophy thesis, my original investigation and achievement has not been submitted by me for the award of any other degree on this work in any other Institution/University.

| DATE:                                           | SHAILY MITTAL                                |

|-------------------------------------------------|----------------------------------------------|

|                                                 | (Enrollment No.: 106208)                     |

|                                                 |                                              |

|                                                 |                                              |

|                                                 |                                              |

| I certify that I have read this thesis and that | in my opinion; it is fully adequate in scope |

| and quality as a thesis for the award of deg    | ree of the Doctor of Science in Computer     |

| Science and Engineering.                        |                                              |

DATE: DR. NITIN (ADVISOR)

### **ACKNOWLEDGEMENTS**

I sincerely express my gratitude to my advisor, Dr. Nitin, for consistent guidance in this research work. I am fortunate to have blessings of almighty, brought closer to my advisor, is always interested in exploring new research directions and ideas with deep vision, encouragement and dimension. He gave freedom in performing research activities and ensured that my various contents are neatly tied together. He has personal touch and support to all his students. One can easily feel friend and philosopher in his disposition.

This research has benefited from the ideas and suggestions of many well wishers. Special thanks to Management, Jaypee Sewa Sansthan especially to Dr. Yajulu Medury, COO–Jaypee Education System & founder Vice Chancellor, Brig. Balbir Singh (Retd.), Director and Prof.(Brig.) S.P.Ghera, HOD CSE department, Jaypee University of Information Technology, Waknaghat, for providing excellent research environment and learning ambiance at the campus.

I am eternally grateful to my respected Mother, Father, Mother-in-law, Father-in-law and affectionate younger Brother and Sister-in law beyond words and for the most devoted and supportive Husband for his love and support he have given me all over these years. Without their sustained moral support, it would have been impossible to succeed in writing this wonderful thesis.

Shaily Mittal

## LIST OF FIGURES

| FIGURE NO.  | FIGURE NAME                                                | PAGE |

|-------------|------------------------------------------------------------|------|

|             |                                                            | NO.  |

| Figure 1.1  | CPU organization                                           | 2    |

| Figure 1.2  | A basic main memory to cache memory mapping scheme         | 3    |

| Figure 1.3  | Direct mapping arrangement                                 | 4    |

| Figure 1.4  | Fully associative mapping arrangement                      | 5    |

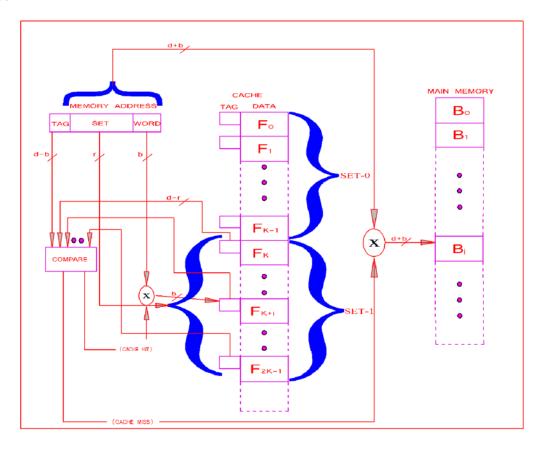

| Figure 1.5  | Set associative mapping arrangement                        | 6    |

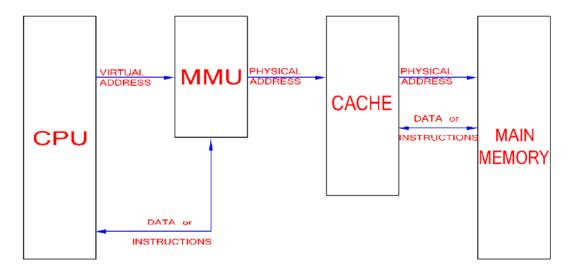

| Figure 1.6  | A unified cache accessed by physical address               | 8    |

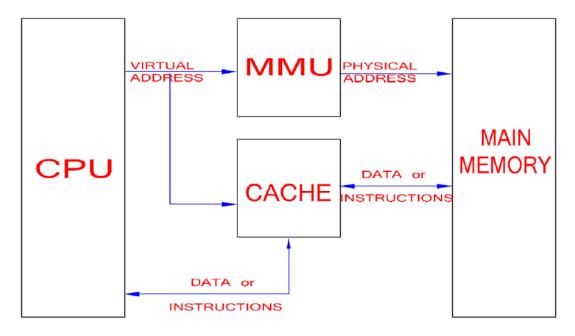

| Figure 1.7  | A unified cache accessed by virtual address                | 9    |

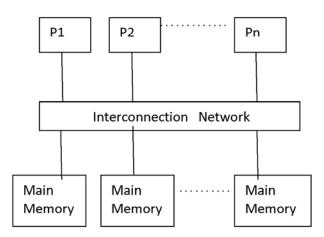

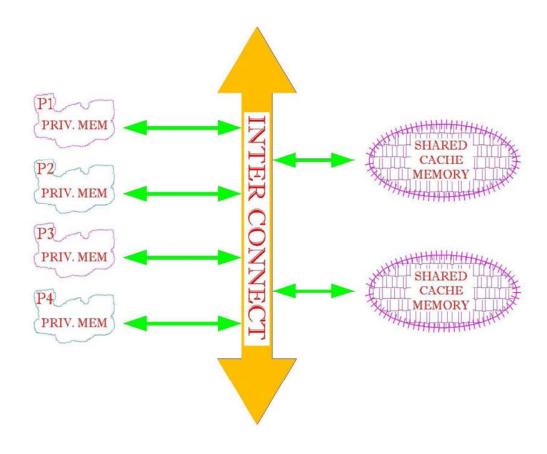

| Figure 1.8  | Architecture of multiprocessor system with shared memories | 11   |

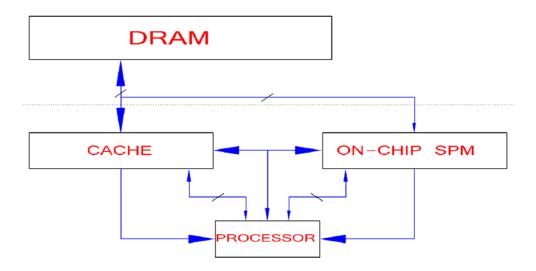

| Figure 1.9  | System architecture with on-chip and off-chip memory       | 15   |

|             | organization                                               |      |

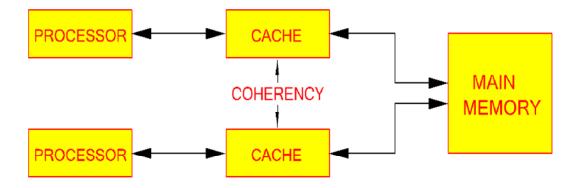

| Figure 1.10 | Cache coherency                                            | 16   |

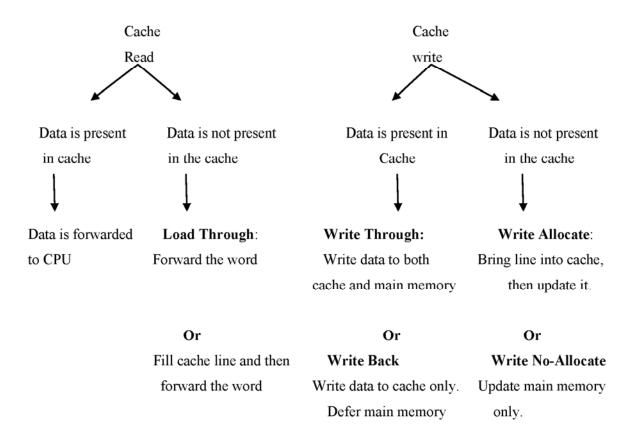

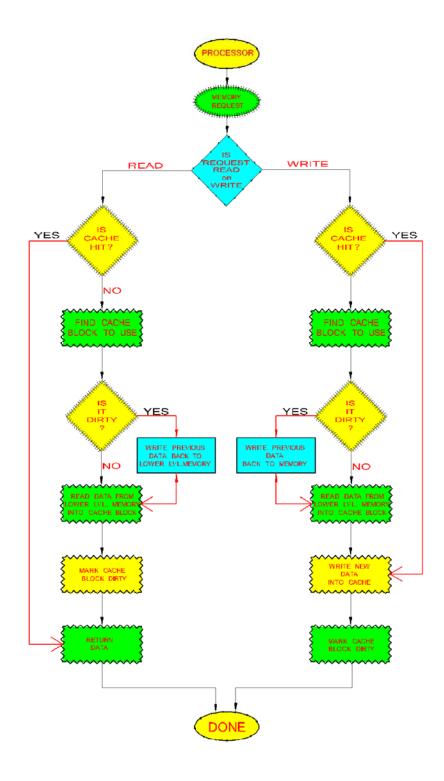

| Figure 1.11 | Types of cache access and their methods                    | 17   |

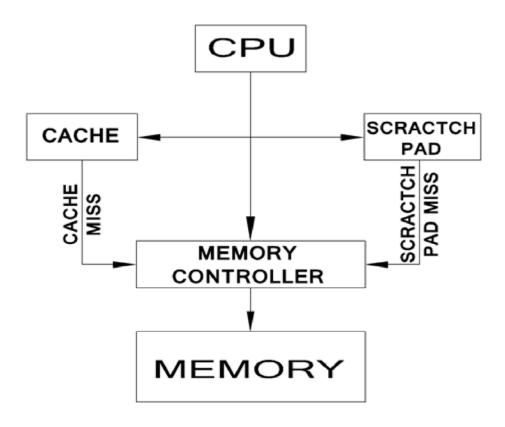

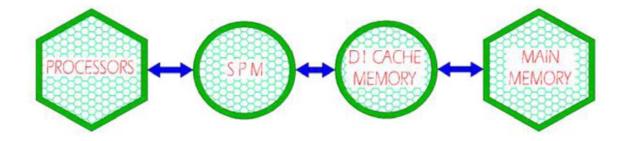

| Figure 1.12 | SPM and cache organization in SoC                          | 19   |

| Figure 3.1  | Semaphore algorithm                                        | 33   |

| Figure 3.2  | Architecture implemented on simulator for evaluation of    | 35   |

|             | locks, transactions and semaphores.                        |      |

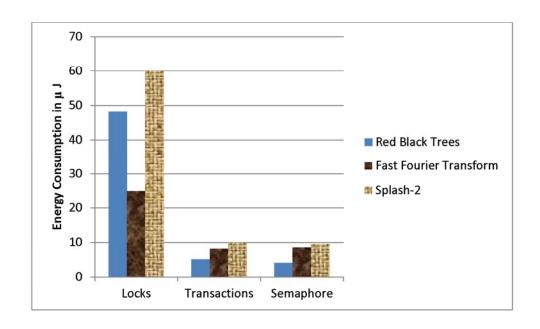

| Figure 3.3  | Energy consumption by the use of locks, transactions and   | 37   |

|             | semaphores                                                 |      |

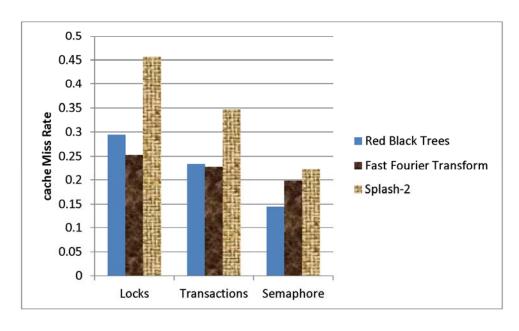

| Figure 3.4  | Cache miss rate by the use of locks, transactions and      | 37   |

|             | semaphores                                                 |      |

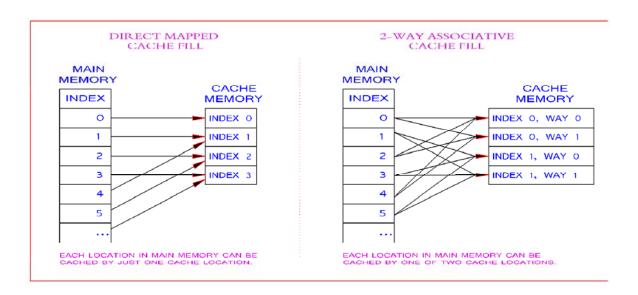

| Figure 4.1  | Cache associativity: direct mapped and 2-way associative   | 41   |

|             | cache                                                      |      |

| Figure 4.2  | Algorithm for proposed SPM replacement policy              | 43   |

| Figure 4.3  | Two level architecture implemented for SPM replacement     | 44   |

|             | policy evaluation                                          |      |

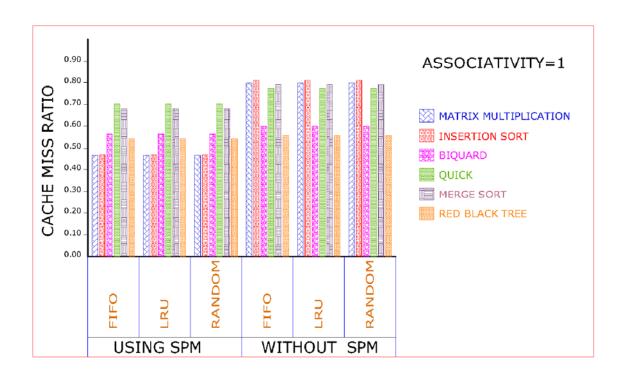

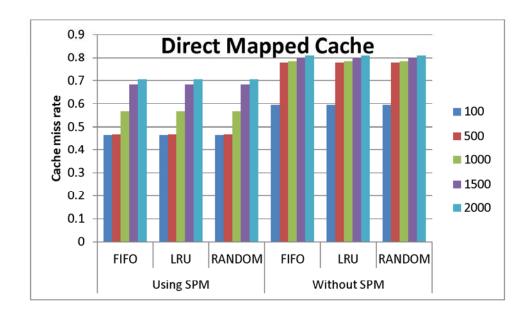

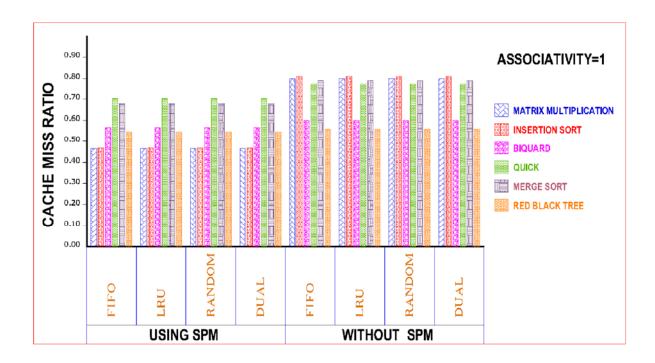

| Figure 4.4  | Direct mapped: cache miss rate with SPM and without SPM    | 46   |

|             | using 6 benchmarks                                         |      |

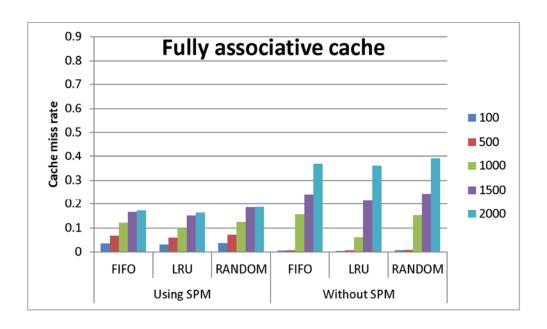

| Figure 4.5  | Fully associative: cache miss rate with SPM and without      | 46 |

|-------------|--------------------------------------------------------------|----|

|             | SPM using 6 benchmarks                                       |    |

| Figure 4.6  | Cache miss rate for biquad benchmark for different           | 47 |

|             | associativity values                                         |    |

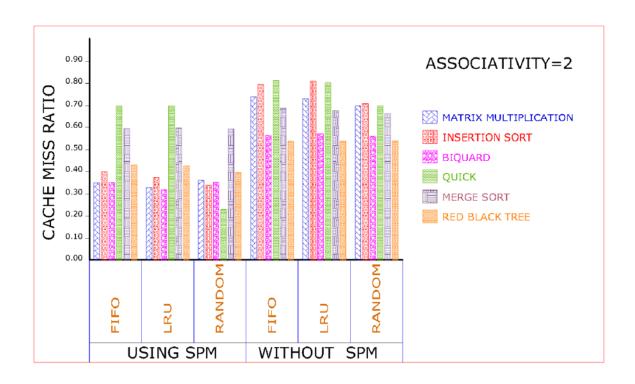

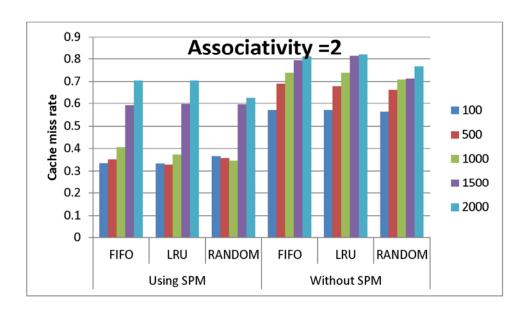

| Figure 4.7  | 2-way associative cache: cache miss rate using SPM and       | 47 |

|             | without using SPM using 6 benchmarks                         |    |

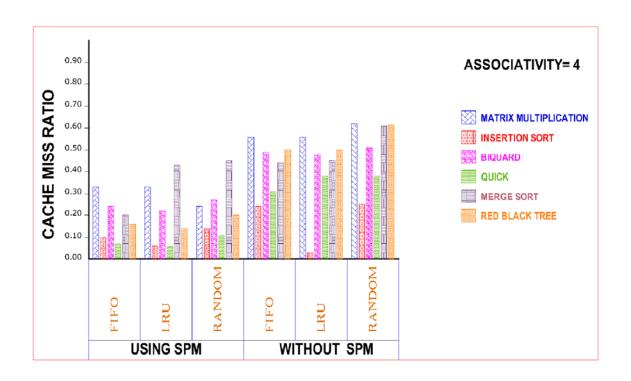

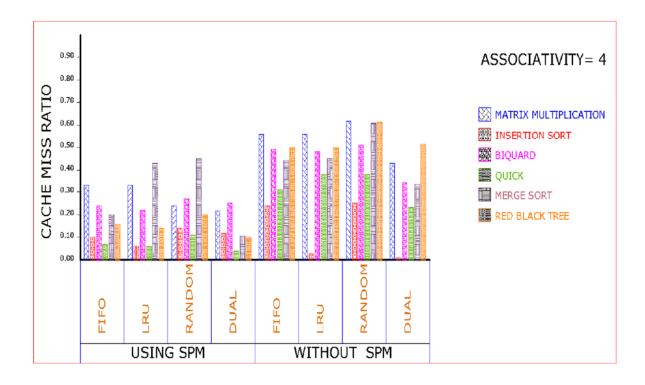

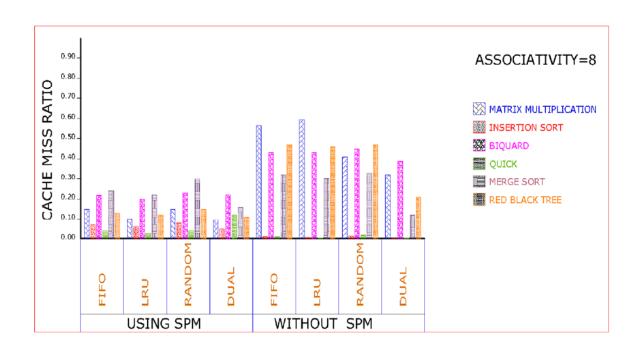

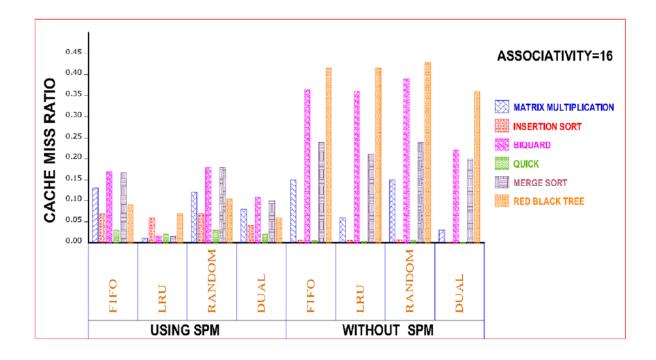

| Figure 4.8  | 4-way associative cache: cache miss rate using SPM and       | 48 |

|             | without using SPM using 6 benchmarks                         |    |

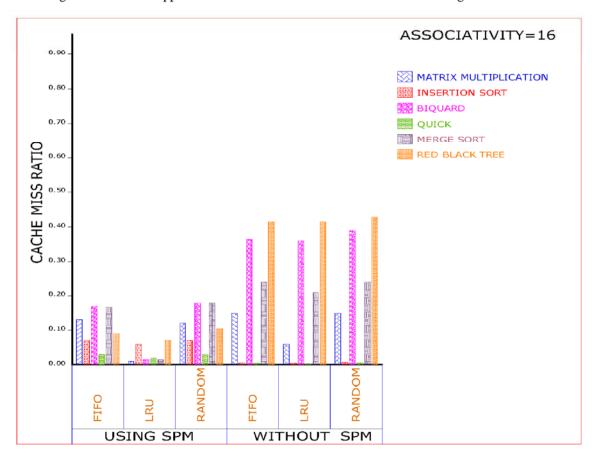

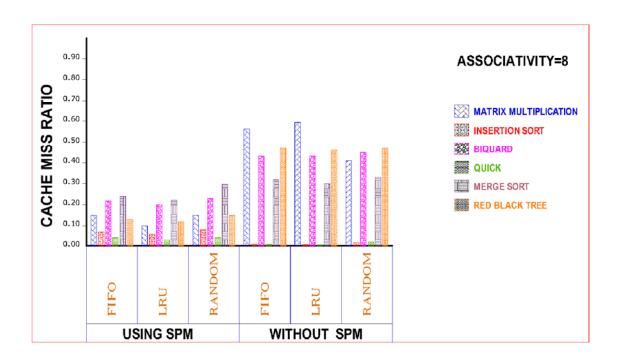

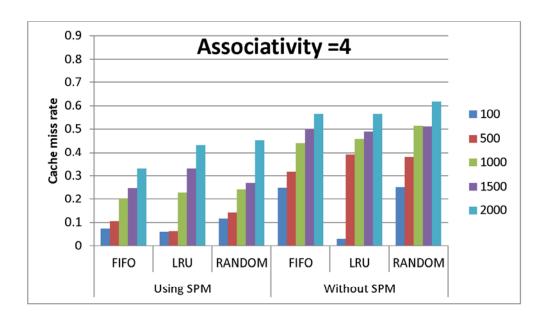

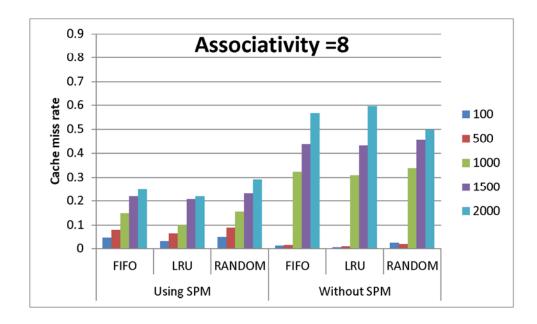

| Figure 4.9  | 8-way associative cache: cache miss rate using SPM and       | 48 |

|             | without using SPM using 6 benchmarks                         |    |

| Figure 4.10 | Cache miss rate for bubble sort with increasing number of    | 50 |

|             | elements in direct mapped cache.                             |    |

| Figure 4.11 | Cache miss rate for bubble sort with increasing number of    | 50 |

|             | elements in 2-way associative cache.                         |    |

| Figure 4.12 | Cache miss rate for bubble sort with increasing number of    | 51 |

|             | elements in 4-way associative cache                          |    |

| Figure 4.13 | Cache miss rate for bubble sort with increasing number of    | 51 |

|             | elements in 8-way associative cache                          |    |

| Figure 4.14 | Cache miss rate for bubble sort with increasing number of    | 52 |

|             | elements in fully associative cache                          |    |

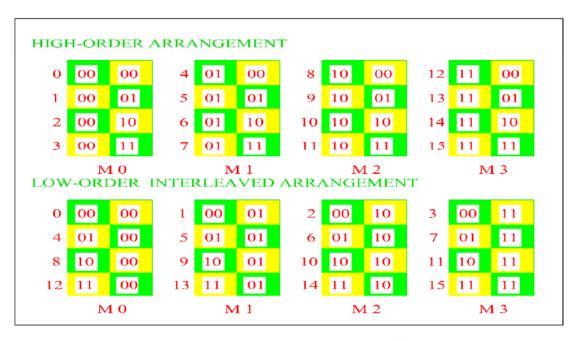

| Figure 5.1  | Interleaved structure                                        | 58 |

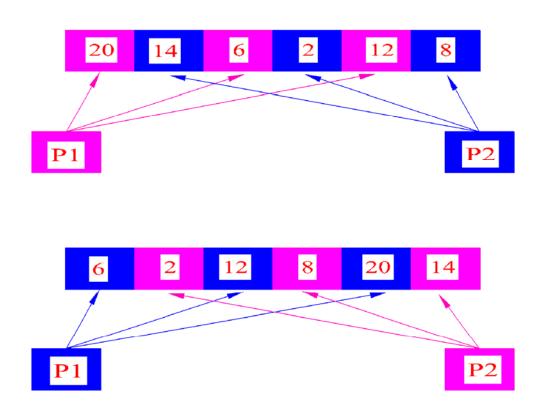

| Figure 5.2  | An example of merge sort using the concept of interleaving   | 58 |

| Figure 5.3  | Modified merge sort, merge and insertion sort algorithms for | 61 |

|             | memory map simulator                                         |    |

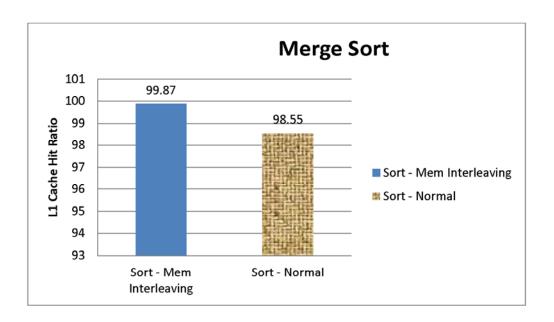

| Figure 5.4  | DL1 (SPM) hit ratio for normal and interleaved merge sort    | 62 |

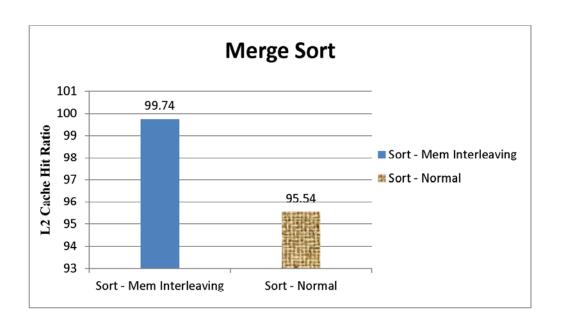

| Figure 5.5  | L2 cache hit ratio for normal and interleaved merge sort     | 63 |

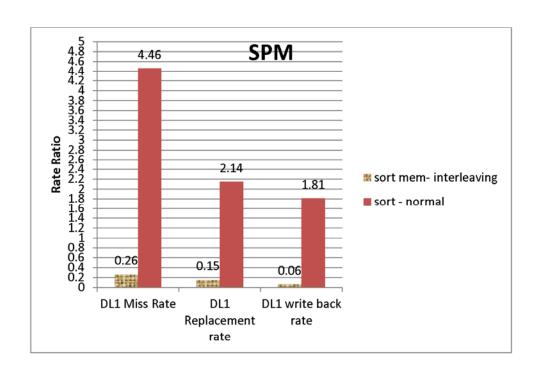

| Figure 5.6  | SPM cache miss rate, replacement rate and write back rate    | 64 |

|             | using merge sort plain and also interleaved                  |    |

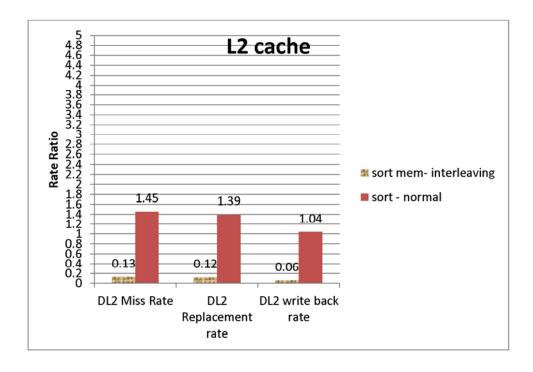

| Figure 5.7  | L2 cache miss rate, replacement rate and write back rate     | 64 |

|             | using merge sort plain and also interleaved                  |    |

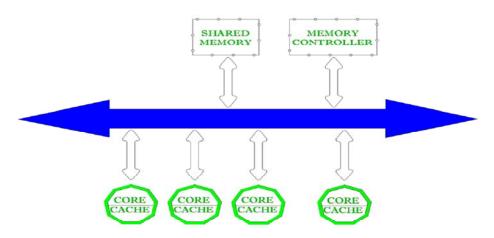

| Figure 5.8  | Architecture used in sorting algorithm evaluation of Simple  | 65 |

|             | Scalar                                                       |    |

| Figure 5.9  | Memory map simulator design                                | 67 |

|-------------|------------------------------------------------------------|----|

| Figure 5.10 | Data flow graph of Memory Map simulator                    | 69 |

| Figure 5.11 | Snapshots of merge sort execution (non-interleaved and     | 70 |

|             | interleaved) on Memory Map simulator with 128 Byte block   |    |

|             | size                                                       |    |

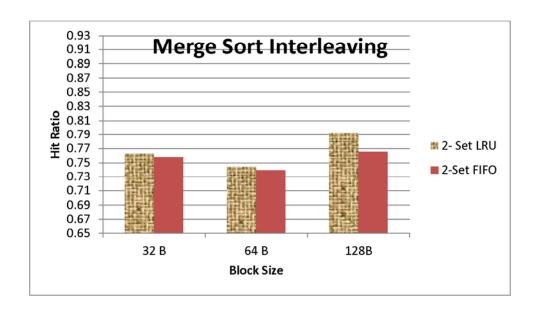

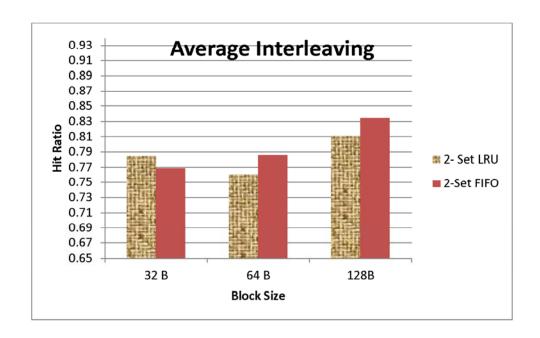

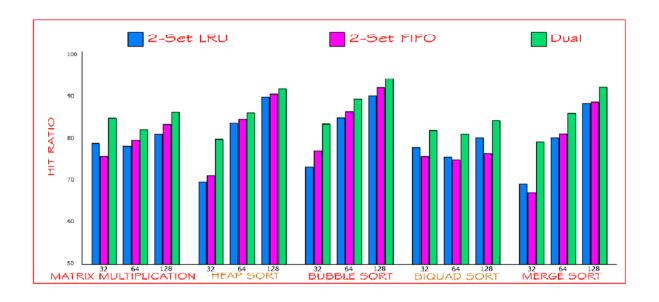

| Figure 5.12 | Hit ratio of 2-set LRU and FIFO replacement policies using | 71 |

|             | merge sort interleaving                                    |    |

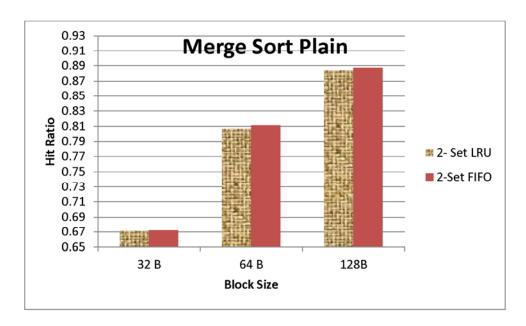

| Figure 5.13 | Hit ratio of 2-set LRU and FIFO replacement policies in    | 71 |

|             | merge sort without interleaved memory                      |    |

| Figure 5.14 | Snapshots of bubble sort execution (non-interleaved and    | 72 |

|             | interleaved) on Memory Map simulator with 32 Byte block    |    |

|             | size                                                       |    |

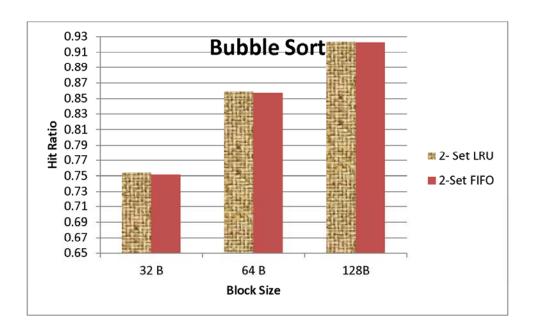

| Figure 5.15 | Hit ratio of 2-set LRU and FIFO replacement policies using | 73 |

|             | bubble sort                                                |    |

| Figure 5.16 | Snapshots of average calculation of 30 elements execution  | 73 |

|             | (non-interleaved and interleaved) on Memory Map simulator  |    |

|             | with 32 Byte block size                                    |    |

| Figure 5.17 | Hit ratio of 2-set LRU and FIFO replacement policies using | 74 |

|             | interleaved average                                        |    |

| Figure 5.18 | Hit ratio of 2-set LRU and FIFO replacement policies using | 74 |

|             | average plain.                                             |    |

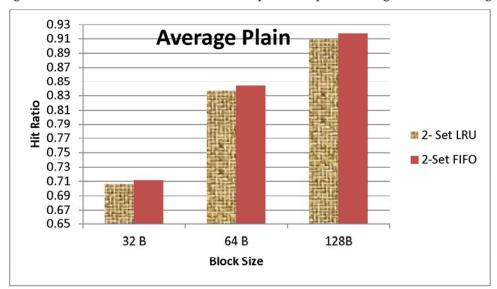

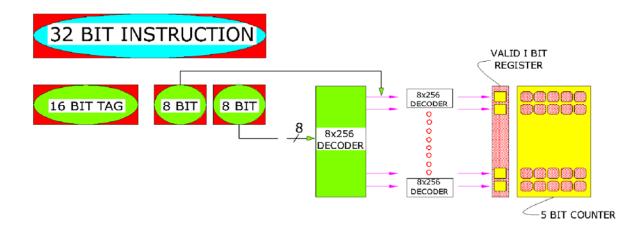

| Figure 6.1  | Architecture of proposed tag based dual replacement policy | 78 |

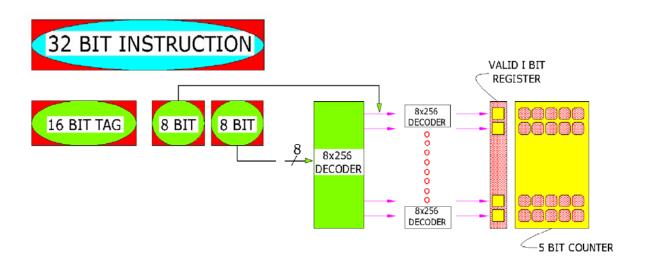

| Figure 6.2  | Hit ratio of 32B, 64B and 128 B block size of LRU, FIFO    | 80 |

|             | and dual replacement policies                              |    |

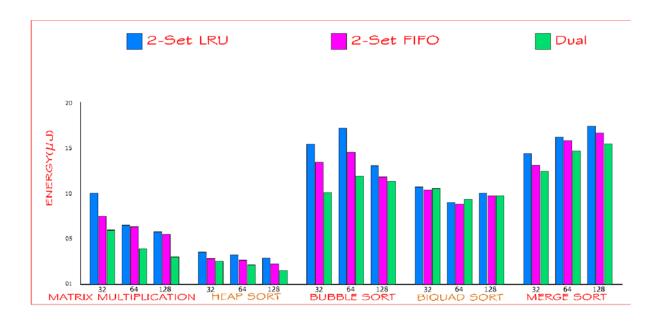

| Figure 6.3  | Energy estimation (µJ) of 32B, 64B and 128 B block size of | 80 |

|             | LRU, FIFO and dual replacement policies                    |    |

| Figure 7.1  | Architecture of proposed tag based dual replacement policy | 86 |

|             | in SPM                                                     |    |

| Figure 7.2  | Cache miss rate for FIFO, LRU, random and dual             | 88 |

|             | replacement policies using and without using SPM           |    |

|             | implementing 6 benchmarks for direct mapped associative    |    |

|             | cache                                                      |    |

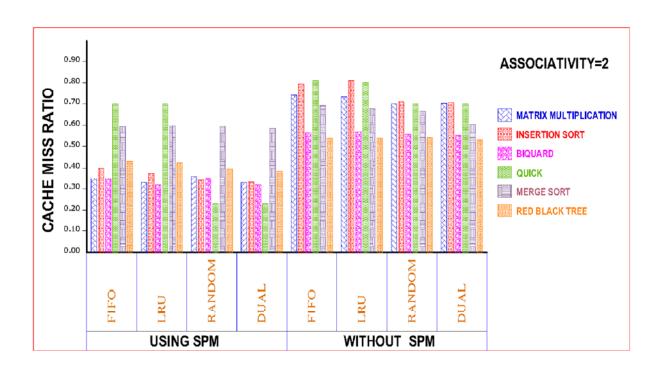

| Figure 7.3  | Cache miss rate for FIFO, LRU, random and dual               | 89  |

|-------------|--------------------------------------------------------------|-----|

|             | replacement policies using and without using SPM             |     |

|             | implementing 6 benchmarks for 2-way associative cache.       |     |

| Figure 7.4  | Cache miss rate for FIFO, LRU, random and dual               | 89  |

|             | replacement policies using and without using SPM             |     |

|             | implementing 6 benchmarks for 4-way associative cache        |     |

| Figure 7.5  | Cache miss rate for FIFO, LRU, random and dual               | 90  |

|             | replacement policies using and without using SPM             |     |

|             | implementing 6 benchmarks for 8-way associative cache.       |     |

| Figure 7.6  | Cache miss rate for FIFO, LRU, random and dual               | 90  |

|             | replacement policies using and without using SPM             |     |

|             | implementing 6 benchmarks for fully associative cache.       |     |

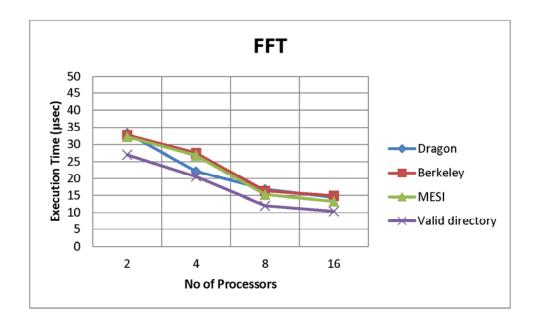

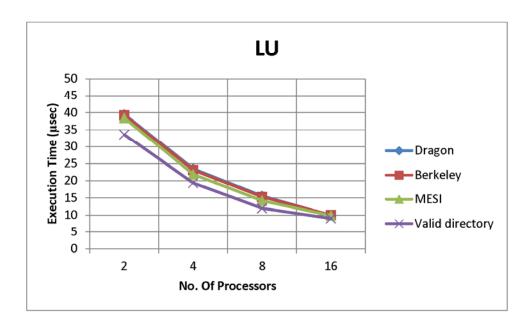

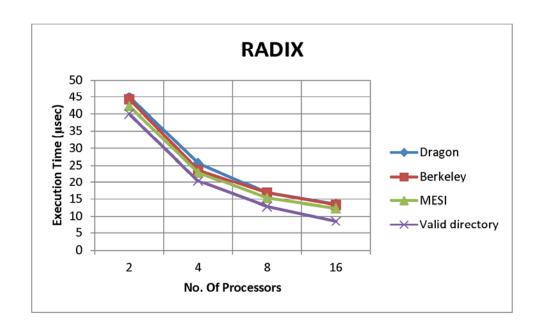

| Figure 8.1  | Execution cycles in FFT with Dragon, Berkeley, MESI and      | 97  |

|             | Valid directory cache coherence protocols                    |     |

| Figure 8.2  | Execution cycles in LU with Dragon, Berkeley, MESI and       | 98  |

|             | Valid directory cache coherence protocols                    |     |

| Figure 8.3  | Execution cycles in OCEAN with Dragon, Berkeley, MESI        | 99  |

|             | and Valid directory cache coherence protocols                |     |

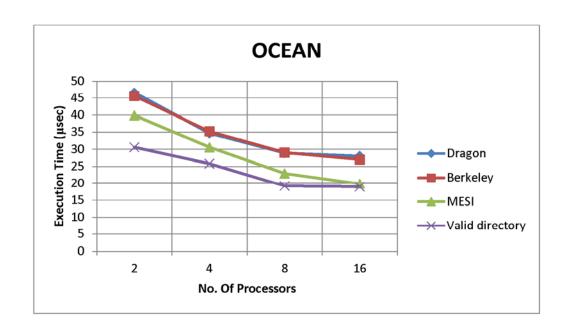

| Figure 8.4  | Execution cycles in RADIX with Dragon, Berkeley, MESI        | 100 |

|             | and Valid directory cache coherence protocols                |     |

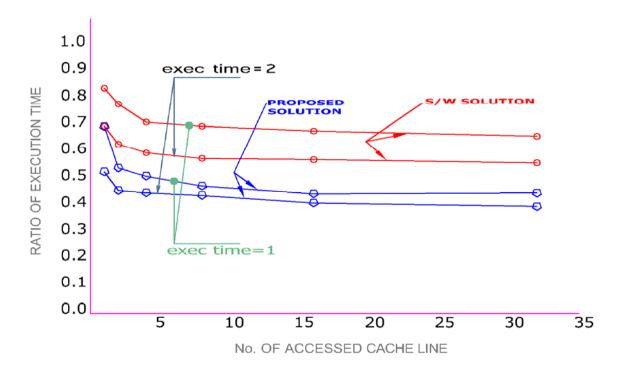

| Figure 8.5  | Ratio of execution times for proposed valid directory vs s/w | 101 |

|             | based cache coherence solution                               |     |

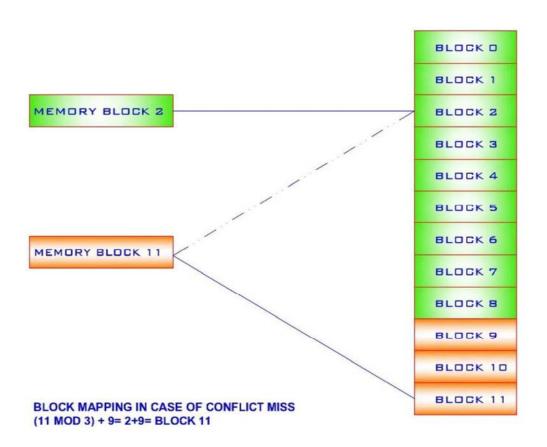

| Figure 9.1  | Fraction associative mapping explanation                     | 108 |

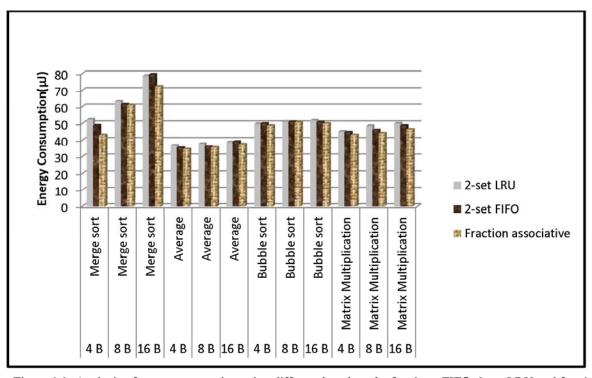

| Figure 9.2  | Analysis of energy conversion using different benchmarks     | 108 |

|             | for 2-set FIFO, 2-set LRU and fraction associative mapping   |     |

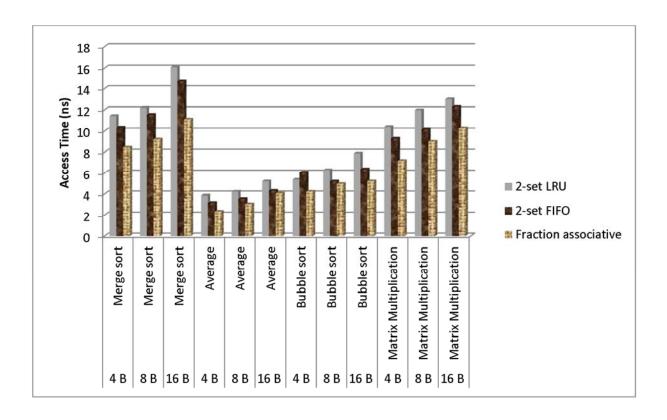

| Figure 9.3  | Analysis of access time using different benchmarks for 2-set | 109 |

|             | FIFO, 2-set LRU and fraction associative mapping             |     |

| Figure 10.1 | MPSoC Architecture                                           | 115 |

| Figure 10.2 | Single bus architecture in MPSoC                             | 116 |

| Figure 10.3 | Network architecture in MPSoC                                | 117 |

| Figure 10.4 | A 4 x 4 mesh topology                                        | 118 |

| Figure 10.5 | A 4 x 4 torus topology                                       | 119 |

| Figure 10.6  | A 4 x 4 BFT topology                                         | 120 |

|--------------|--------------------------------------------------------------|-----|

| Figure 10.7  | A 4 x 4 EBFT topology                                        | 121 |

| Figure 10.8  | Throughput vs network load for flit length=10 in dijkstra's  | 129 |

|              | algorithm using BFT, mesh, torus and EBFT topologies         |     |

| Figure 10.9  | Throughput vs network load for flit length=32 in dijkstra's  | 130 |

|              | algorithm using BFT, mesh, torus and EBFT topologies         |     |

| Figure 10.10 | Latency vs network load for flit length=10 in dijkstra's     | 132 |

|              | algorithm using BFT, mesh, torus and EBFT topologies         |     |

| Figure 10.11 | Latency vs network load for flit length=32 in dijkstra's     | 132 |

|              | algorithm using BFT, mesh, torus and EBFT topologies         |     |

| Figure 10.12 | Throughput vs network load for flit length=10 in distance    | 134 |

|              | vector algorithm using BFT, mesh, torus and EBFT             |     |

|              | topologies                                                   |     |

| Figure 10.13 | Throughput vs network load for flit length=32 in distance    | 135 |

|              | vector algorithm using BFT, mesh, torus and EBFT             |     |

|              | topologies                                                   |     |

| Figure 10.14 | Average packet delay vs network load for flit length=10 in   | 136 |

|              | distance vector algorithm using BFT, mesh, torus and EBFT    |     |

|              | topologies                                                   |     |

| Figure 10.15 | Average packet delay vs network load for flit length=32 in   | 136 |

|              | distance vector algorithm using BFT, mesh, torus and EBFT    |     |

|              | topologies                                                   |     |

| Figure 10.16 | Throughput with increase in network size (packet size = 10   | 137 |

|              | flits)                                                       |     |

| Figure 10.17 | Throughput with increase in network size (packet size = 32   | 138 |

|              | flits)                                                       |     |

| Figure 10.18 | Average latency with increase in network size (packet size = | 138 |

|              | 10 flits)                                                    |     |

| Figure 10.19 | Average latency with increase in network size (packet size = | 139 |

|              | 32 flits)                                                    |     |

### LIST OF TABLES

| TABLE NO. | TABLE NAME                                                          | PAGE |

|-----------|---------------------------------------------------------------------|------|

|           |                                                                     | NO.  |

| Table 3.1 | Energy consumption in $\mu J$ for locks, transactions and semaphore | 37   |

| Table 3.2 | Cache miss rate obtained using locks, transactions and semaphore    | 38   |

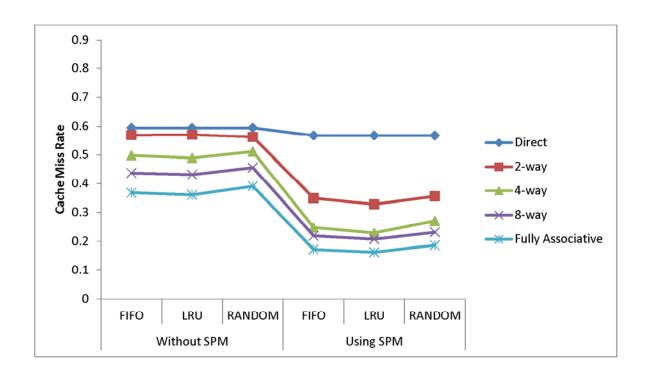

| Table 4.1 | Average miss rate comparison for cache vs SPM using LRU,            | 49   |

|           | FIFO, and random replacement policies                               |      |

| Table 5.1 | Experimental results calculating hit ratio for 2-set LRU and 2-     | 75   |

|           | set FIFO using block sizes 32, 64 and 128 B on different            |      |

|           | algorithms                                                          |      |

| Table 6.1 | Cache configurations used in evaluating cache hit ratio and         | 79   |

|           | power for comparing tag based dual replacement policy to            |      |

|           | LRU and FIFO in Simple Scalar simulator                             |      |

| Table 7.1 | Cache configurations used in Simple Scalar tool for                 | 88   |

|           | comparing tag based dual replacement policy to LRU, FIFO            |      |

|           | and random in SPM.                                                  |      |

| Table 7.2 | Cache miss rate values for FIFO, LRU, random and TDMRP              | 91   |

|           | in SPM and cache                                                    |      |

| Table 8.1 | Simulation environment for evaluating execution time for            | 97   |

|           | Dragon, Berkeley, MESI and Valid directory cache coherence          |      |

|           | protocol in LIMES simulator                                         |      |

| Table 8.2 | Execution time ( $\mu sec$ ) of Dragon, Berkeley, MESI and Valid    | 98   |

|           | directory cache coherence protocols using FFT benchmark in          |      |

|           | LIMES simulator                                                     |      |

| Table 8.3 | Execution time (µsec) of Dragon, Berkeley, MESI and Valid           | 98   |

|           | directory cache coherence protocols using LU benchmark              |      |

|           | inLIMES simulator                                                   |      |

| Table 8.4 | Execution time (µsec) of Dragon, Berkeley, MESI and Valid           | 99   |

|            | directory cache coherence protocols using OCEAN                |     |

|------------|----------------------------------------------------------------|-----|

|            | benchmark in LIMES simulator                                   |     |

| Table 8.5  | Execution time (µsec) of Dragon, Berkeley, MESI and Valid      | 100 |

|            | directory cache coherence protocols using RADIX benchmark      |     |

|            | in LIMES simulator                                             |     |

| Table 8.6  | Simulation environment in seamless CVE to evaluate ratio of    | 100 |

|            | execution time                                                 |     |

| Table 8.7  | Experimental values for ratio of execution time for directory  | 102 |

|            | protocol vs. proposed solution                                 |     |

| Table 9.1  | Experimental values for energy consumption using fraction      | 109 |

|            | associative mapping                                            |     |

| Table 9.2  | Experimental values for access time using fraction associative | 110 |

|            | mapping                                                        |     |

| Table 10.1 | Simulation environment for measuring effect of network load    | 128 |

|            | on two protocols                                               |     |

| Table 10.2 | Simulation environment for measuring effect of network size    | 128 |

|            | on two protocols                                               |     |

| Table 10.3 | Simulation results for throughput and average packet delay     | 131 |

|            | with flit length 10 and 32 in BFT, mesh, torus and EBFT        |     |

|            | topologies using dijkstra's algorithm in NoC                   |     |

| Table 10.4 | Simulation results for throughput and average packet delay     | 133 |

|            | with flit length 10 and 32 in BFT, mesh, torus and EBFT        |     |

|            | topologies using Distance vector algorithm in NoC              |     |

### CANDIDATE'S DECLARATION

I hereby certify that the work, which is being presented here in the thesis entitled, MEMORY CUSTOMIZATION IN MULTIPROCESSOR SYSTEMS-ON-CHIP, submitted in partial fulfillment of the requirements for the award of the degree of Doctor of Philosophy in Computer Science & Engineering and submitted in Department of Computer Science & Engineering and Information Technology, Jaypee University of Technology (JUIT), Solan is an authentic record of my own work carried out (July 2010–April 2014) under the supervision and guidance of Dr. Nitin, Associate Professor, Department of Computer Science & Engineering and Information Technology Chancellor, JUIT, Solan.

I hereby declare that this Doctor of Philosophy thesis, my original investigation and achievement has not been submitted by me for the award of any other degree on this work in any other Institution/University.

| DATE:                                        | SHAILY MITTAL                                    |

|----------------------------------------------|--------------------------------------------------|

|                                              | (Enrollment No.: 106208)                         |

|                                              |                                                  |

|                                              |                                                  |

|                                              |                                                  |

| I certify that I have read this thesis and t | hat in my opinion; it is fully adequate in scope |

| and quality as a thesis for the award of     | degree of the Doctor of Science in Computer      |

DATE:

DR. NITIN

(ADVISOR)

Science and Engineering.

## TABLE OF CONTENTS

|                                           | PAGE NO. |

|-------------------------------------------|----------|

| CANDIDATE'S DECLARATION                   | iii      |

| ABSTRACT                                  | iv-vi    |

| LIST OF FIGURES                           | vii–xi   |

| LIST OF TABLES                            | xii-xiii |

| ACKNOWLEDGEMENTS                          | xiv      |

| CONTENTS                                  | xvi–xx   |

| CHAPTER 1                                 | 1–21     |

| INTRODUCTION                              |          |

| 1.1 Embedded Systems                      | 1        |

| 1.2 Cache Memory Overview                 | 2        |

| 1.2.1 Unit of Transfer                    | 3        |

| 1.2.2 Locality of Reference               | 6        |

| 1.2.3 Replacement Policy                  | 7        |

| 1.2.4 Cache Addressing Models             | 8        |

| 1.2.5 Memory Capacity Planning            | 9        |

| 1.3 Systems on Chip                       | 10       |

| 1.4 Multiprocessor Systems on Chip        | 11       |

| 1.5 Memory Organization                   | 12       |

| 1.6 Current Issues of Cache Memory Access | 15       |

| 1.6.1 Multiple Processor Synchronization  | 15       |

| 1.6.2 Processor-Memory Speed Gap          | 15       |

| 1.6.3 Cache Coherence                     | 16       |

| 1.6.4 Power/Energy Consumption            | 17       |

| 1.7 SPM                                   | 19       |

| 1.8 Dissertation Contribution and Outline | 19       |

| CHAPTER 2                                                 | 22-29 |

|-----------------------------------------------------------|-------|

| LITERATURE REVIEW                                         |       |

|                                                           |       |

| CHAPTER 3                                                 | 30-38 |

| A RESOLUTION FOR SHARED MEMORY CONFLICT IN                |       |

| MULTIPROCESSOR SYSTEM-ON-A-CHIP                           |       |

| 3.1 Introduction                                          | 30    |

| 3.2 Related Eork                                          | 31    |

| 3.3 Semaphores                                            | 32    |

| 3.4 Simulation Environment                                | 34    |

| 3.5 Experimental Results                                  | 36    |

| 3.6 Conclusion and Future Work                            | 38    |

| CHAPTER 4                                                 | 39-53 |

| REPLACEMENT POLICIES FOR SCRATCH PAD MEMORY IN            |       |

| EMBEDDED SYSTEMS                                          |       |

| 4.1 Introduction                                          | 39    |

| 4.2 Problem Description                                   | 41    |

| 4.3 Proposed Solution                                     | 43    |

| 4.4 Experimental Environment                              | 44    |

| 4.5 Results                                               | 45    |

| 4.6 Conclusion and Future Work                            | 52    |

| CHAPTER 5                                                 | 54-75 |

| MEMORY MAP: A MULTIPROCESSOR CACHE SIMULATOR              |       |

| 5.1 Introduction                                          | 54    |

| 5.2 Survey and Motivation                                 | 56    |

| 5.3 Alternate approach for multiprocessor synchronization | 57    |

| 5.3.1 Memory Interleaving                                 | 57    |

| 5.3.2 Observations                                 | 62     |

|----------------------------------------------------|--------|

| 5.3.3 Limitations                                  | 65     |

| 5.4 Architecture of Memory Map simulator           | 65     |

| 5.5 Test bed and Experimental Setup                | 67     |

| 5.6 Experimental Results                           | 68     |

| 5.7 Conclusion and Future Work                     | 75     |

| CHAPTER 6                                          | 76-82  |

| AN EFFICIENT TAG-BASED DUAL MAPPING REPLACEMENT    |        |

| POLICY                                             |        |

| 6.1 Introduction                                   | 76     |

| 6.2 Proposed Replacement Policy                    | 77     |

| 6.3 Experimental Methodology and Results           | 78     |

| 6.3.1 Cache Configuration and Benchmarks           | 78     |

| 6.3.2 Experimental Evaluation                      | 79     |

| 6.4 Conclusion and Future Work                     | 81     |

| CHAPTER 7                                          | 83-92  |

| A NEW EFFICIENT REPLACEMENT POLICY FOR SCRATCH PAD |        |

| MEMORY                                             |        |

| 7.1 Introduction and Motivation                    | 83     |

| 7.2 Proposed Policy                                | 85     |

| 7.3 Experimental Setup and Evaluation              | 86     |

| 7.4 Observations                                   | 87     |

| 7.5 Conclusion and Future Work                     | 92     |

| CHAPTER 8                                          | 93-103 |

| A NOVEL DIRECTORY BASED SOLUTION TO CACHE          |        |

| COHERENCE PROBLEM                                  |        |

| 8.1 Introduction and Motivation                                        | 93      |

|------------------------------------------------------------------------|---------|

| 8.2 Survey and Motivation                                              | 94      |

| 8.3 Proposed Solution                                                  | 95      |

| 8.4 Experimental Setup and Test bed                                    | 96      |

| 8.5 Comparative Analysis of Valid Directory, DRAGON, BERKELEY AND MESI | 96      |

| 8.6 Experimental setup for ratio of execution time evaluation          | 100     |

| 8.7 Conclusion and Future Work                                         | 102     |

| CHAPTER 9                                                              | 104-111 |

| FRACTIONAL ASSOCIATIVE MEMORY: A SOLUTION TO                           |         |

| CONFLICT MISSES                                                        |         |

| 9.1 Introduction and Motivation                                        | 104     |

| 9.2 Related Work                                                       | 105     |

| 9.3 Fraction Associative Memory                                        | 106     |

| 9.4 Test bed and Experimental Setup                                    | 110     |

| 9.5 Results and Discussions                                            | 110     |

| 9.6 Conclusion                                                         | 111     |

| CHAPTER 10                                                             | 112-140 |

| COMMUNICATION ISSUES IN MULTIPROCESSOR SYSTEM-ON-                      |         |

| CHIP: PERFORMANCE AND POWER                                            |         |

| 10.1 Introduction and Motivation                                       | 112     |

| 10.2 MPSoC Architecture                                                | 114     |

| 10.3 Network on Chip (NoC)                                             | 114     |

| 10.4 Topologies in NoC                                                 | 117     |

| 10.4.1 Mesh network                                                    | 118     |

| 10.4.2 Torus                                                           | 118     |

| 10.4.3 Butterfly Fat Tree                                              | 119     |

| 10.4.4 Extended Butterfly Fat Tree                                     | 120     |

| 10.5 Routing Algorithm                                         | 121     |

|----------------------------------------------------------------|---------|

| 10.6 Dijkstra static routing algorithm                         | 122     |

| 10.7 Distance vector dynamic routing protocol                  | 124     |

| 10.8 Problem Formulation                                       | 126     |

| 10.9 Experimental Setup and Test bed                           | 127     |

| 10.10 Analysis of effect of network load and routing algorithm | 129     |

| 10.11Analysis of effect of network size                        | 137     |

| 10.12Conclusion and Future Scope                               | 139     |

|                                                                |         |

| CHAPTER 11                                                     | 141-143 |

| CONCLUSION AND FUTURE DISCUSSIONS                              |         |

|                                                                |         |

| 11.1Conclusion                                                 | 141     |

| 11.2Future Work                                                | 143     |

|                                                                |         |

| References                                                     | 144-157 |

## TABLE OF CONTENTS

|                                           | PAGE NO. |

|-------------------------------------------|----------|

| CANDIDATE'S DECLARATION                   | iii      |

| ABSTRACT                                  | iv-vi    |

| LIST OF FIGURES                           | vii–xi   |

| LIST OF TABLES                            | xii-xiii |

| ACKNOWLEDGEMENTS                          | xiv      |

| CONTENTS                                  | xvi–xx   |

| CHAPTER 1                                 | 1–21     |

| INTRODUCTION                              |          |

| 1.1 Embedded Systems                      | 1        |

| 1.2 Cache Memory Overview                 | 2        |

| 1.2.1 Unit of Transfer                    | 3        |

| 1.2.2 Locality of Reference               | 6        |

| 1.2.3 Replacement Policy                  | 7        |

| 1.2.4 Cache Addressing Models             | 8        |

| 1.2.5 Memory Capacity Planning            | 9        |

| 1.3 Systems on Chip                       | 10       |

| 1.4 Multiprocessor Systems on Chip        | 11       |

| 1.5 Memory Organization                   | 12       |

| 1.6 Current Issues of Cache Memory Access | 15       |

| 1.6.1 Multiple Processor Synchronization  | 15       |

| 1.6.2 Processor-Memory Speed Gap          | 15       |

| 1.6.3 Cache Coherence                     | 16       |

| 1.6.4 Power/Energy Consumption            | 17       |

| 1.7 SPM                                   | 19       |

| 1.8 Dissertation Contribution and Outline | 19       |

| CHAPTER 2                                                 | 22-29 |

|-----------------------------------------------------------|-------|

| LITERATURE REVIEW                                         |       |

|                                                           |       |

| CHAPTER 3                                                 | 30-38 |

| A RESOLUTION FOR SHARED MEMORY CONFLICT IN                |       |

| MULTIPROCESSOR SYSTEM-ON-A-CHIP                           |       |

| 3.1 Introduction                                          | 30    |

| 3.2 Related Eork                                          | 31    |

| 3.3 Semaphores                                            | 32    |

| 3.4 Simulation Environment                                | 34    |

| 3.5 Experimental Results                                  | 36    |

| 3.6 Conclusion and Future Work                            | 38    |

| CHAPTER 4                                                 | 39-53 |

| REPLACEMENT POLICIES FOR SCRATCH PAD MEMORY IN            |       |

| EMBEDDED SYSTEMS                                          |       |

| 4.1 Introduction                                          | 39    |

| 4.2 Problem Description                                   | 41    |

| 4.3 Proposed Solution                                     | 43    |

| 4.4 Experimental Environment                              | 44    |

| 4.5 Results                                               | 45    |

| 4.6 Conclusion and Future Work                            | 52    |

| CHAPTER 5                                                 | 54-75 |

| MEMORY MAP: A MULTIPROCESSOR CACHE SIMULATOR              |       |

| 5.1 Introduction                                          | 54    |

| 5.2 Survey and Motivation                                 | 56    |

| 5.3 Alternate approach for multiprocessor synchronization | 57    |

| 5.3.1 Memory Interleaving                                 | 57    |

| 5.3.2 Observations                                 | 62     |

|----------------------------------------------------|--------|

| 5.3.3 Limitations                                  | 65     |

| 5.4 Architecture of Memory Map simulator           | 65     |

| 5.5 Test bed and Experimental Setup                | 67     |

| 5.6 Experimental Results                           | 68     |

| 5.7 Conclusion and Future Work                     | 75     |

| CHAPTER 6                                          | 76-82  |

| AN EFFICIENT TAG-BASED DUAL MAPPING REPLACEMENT    |        |

| POLICY                                             |        |

| 6.1 Introduction                                   | 76     |

| 6.2 Proposed Replacement Policy                    | 77     |

| 6.3 Experimental Methodology and Results           | 78     |

| 6.3.1 Cache Configuration and Benchmarks           | 78     |

| 6.3.2 Experimental Evaluation                      | 79     |

| 6.4 Conclusion and Future Work                     | 81     |

| CHAPTER 7                                          | 83-92  |

| A NEW EFFICIENT REPLACEMENT POLICY FOR SCRATCH PAD |        |

| MEMORY                                             |        |

| 7.1 Introduction and Motivation                    | 83     |

| 7.2 Proposed Policy                                | 85     |

| 7.3 Experimental Setup and Evaluation              | 86     |

| 7.4 Observations                                   | 87     |

| 7.5 Conclusion and Future Work                     | 92     |

| CHAPTER 8                                          | 93-103 |

| A NOVEL DIRECTORY BASED SOLUTION TO CACHE          |        |

| COHERENCE PROBLEM                                  |        |

| 8.1 Introduction and Motivation                                        | 93      |

|------------------------------------------------------------------------|---------|

| 8.2 Survey and Motivation                                              | 94      |

| 8.3 Proposed Solution                                                  | 95      |

| 8.4 Experimental Setup and Test bed                                    | 96      |

| 8.5 Comparative Analysis of Valid Directory, DRAGON, BERKELEY AND MESI | 96      |

| 8.6 Experimental setup for ratio of execution time evaluation          | 100     |

| 8.7 Conclusion and Future Work                                         | 102     |

| CHAPTER 9                                                              | 104-111 |

| FRACTIONAL ASSOCIATIVE MEMORY: A SOLUTION TO                           |         |

| CONFLICT MISSES                                                        |         |

| 9.1 Introduction and Motivation                                        | 104     |

| 9.2 Related Work                                                       | 105     |

| 9.3 Fraction Associative Memory                                        | 106     |

| 9.4 Test bed and Experimental Setup                                    | 110     |

| 9.5 Results and Discussions                                            | 110     |

| 9.6 Conclusion                                                         | 111     |

| CHAPTER 10                                                             | 112-140 |

| COMMUNICATION ISSUES IN MULTIPROCESSOR SYSTEM-ON-                      |         |

| CHIP: PERFORMANCE AND POWER                                            |         |

| 10.1 Introduction and Motivation                                       | 112     |

| 10.2 MPSoC Architecture                                                | 114     |

| 10.3 Network on Chip (NoC)                                             | 114     |

| 10.4 Topologies in NoC                                                 | 117     |

| 10.4.1 Mesh network                                                    | 118     |

| 10.4.2 Torus                                                           | 118     |

| 10.4.3 Butterfly Fat Tree                                              | 119     |

| 10.4.4 Extended Butterfly Fat Tree                                     | 120     |

| 10.5 Routing Algorithm                                         | 121     |

|----------------------------------------------------------------|---------|

| 10.6 Dijkstra static routing algorithm                         | 122     |

| 10.7 Distance vector dynamic routing protocol                  | 124     |

| 10.8 Problem Formulation                                       | 126     |

| 10.9 Experimental Setup and Test bed                           | 127     |

| 10.10 Analysis of effect of network load and routing algorithm | 129     |

| 10.11Analysis of effect of network size                        | 137     |

| 10.12Conclusion and Future Scope                               | 139     |

|                                                                |         |

| CHAPTER 11                                                     | 141-143 |

| CONCLUSION AND FUTURE DISCUSSIONS                              |         |

|                                                                |         |

| 11.1Conclusion                                                 | 141     |

| 11.2Future Work                                                | 143     |

|                                                                |         |

| References                                                     | 144-157 |

## LIST OF TABLES

| TABLE NO. | TABLE NAME                                                                                                                                                               | PAGE |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|           |                                                                                                                                                                          | NO.  |

| Table 3.1 | Energy consumption in $\mu J$ for locks, transactions and semaphore                                                                                                      | 37   |

| Table 3.2 | Cache miss rate obtained using locks, transactions and semaphore                                                                                                         | 38   |

| Table 4.1 | Average miss rate comparison for cache vs SPM using LRU,                                                                                                                 | 49   |

| Table 5.1 | FIFO, and random replacement policies  Experimental results calculating hit ratio for 2-set LRU and 2- set FIFO using block sizes 32, 64 and 128 B on different          | 75   |

| Table 6.1 | algorithms  Cache configurations used in evaluating cache hit ratio and power for comparing tag based dual replacement policy to                                         | 79   |

| Table 7.1 | LRU and FIFO in Simple Scalar simulator  Cache configurations used in Simple Scalar tool for comparing tag based dual replacement policy to LRU, FIFO and random in SPM. | 88   |

| Table 7.2 | Cache miss rate values for FIFO, LRU, random and TDMRP in SPM and cache                                                                                                  | 91   |

| Table 8.1 | Simulation environment for evaluating execution time for Dragon, Berkeley, MESI and Valid directory cache coherence protocol in LIMES simulator                          | 97   |

| Table 8.2 | Execution time (µsec) of Dragon, Berkeley, MESI and Valid directory cache coherence protocols using FFT benchmark in                                                     | 98   |

| Table 8.3 | LIMES simulator  Execution time (µsec) of Dragon, Berkeley, MESI and Valid directory cache coherence protocols using LU benchmark                                        | 98   |

| Table 8.4 | inLIMES simulator  Execution time (µsec) of Dragon, Berkeley, MESI and Valid                                                                                             | 99   |

|            | directory cache coherence protocols using OCEAN                |     |

|------------|----------------------------------------------------------------|-----|

|            | benchmark in LIMES simulator                                   |     |

| Table 8.5  | Execution time (µsec) of Dragon, Berkeley, MESI and Valid      | 100 |

|            | directory cache coherence protocols using RADIX benchmark      |     |

|            | in LIMES simulator                                             |     |

| Table 8.6  | Simulation environment in seamless CVE to evaluate ratio of    | 100 |

|            | execution time                                                 |     |

| Table 8.7  | Experimental values for ratio of execution time for directory  | 102 |

|            | protocol vs. proposed solution                                 |     |

| Table 9.1  | Experimental values for energy consumption using fraction      | 109 |

|            | associative mapping                                            |     |

| Table 9.2  | Experimental values for access time using fraction associative | 110 |

|            | mapping                                                        |     |

| Table 10.1 | Simulation environment for measuring effect of network load    | 128 |

|            | on two protocols                                               |     |

| Table 10.2 | Simulation environment for measuring effect of network size    | 128 |

|            | on two protocols                                               |     |

| Table 10.3 | Simulation results for throughput and average packet delay     | 131 |

|            | with flit length 10 and 32 in BFT, mesh, torus and EBFT        |     |

|            | topologies using dijkstra's algorithm in NoC                   |     |

| Table 10.4 | Simulation results for throughput and average packet delay     | 133 |

|            | with flit length 10 and 32 in BFT, mesh, torus and EBFT        |     |

|            | topologies using Distance vector algorithm in NoC              |     |

## LIST OF FIGURES

| FIGURE NO.  | FIGURE NAME                                                       | PAGE |

|-------------|-------------------------------------------------------------------|------|

|             |                                                                   | NO.  |

| Figure 1.1  | CPU organization                                                  | 2    |

| Figure 1.2  | A basic main memory to cache memory mapping scheme                | 3    |

| Figure 1.3  | Direct mapping arrangement                                        | 4    |

| Figure 1.4  | Fully associative mapping arrangement                             | 5    |

| Figure 1.5  | Set associative mapping arrangement                               | 6    |

| Figure 1.6  | A unified cache accessed by physical address                      | 8    |

| Figure 1.7  | A unified cache accessed by virtual address                       | 9    |

| Figure 1.8  | Architecture of multiprocessor system with shared memories        | 11   |

| Figure 1.9  | System architecture with on-chip and off-chip memory organization | 15   |

| Figure 1.10 | Cache coherency                                                   | 16   |

| Figure 1.11 | Types of cache access and their methods                           | 17   |

| Figure 1.12 | SPM and cache organization in SoC                                 | 19   |

| Figure 3.1  | Semaphore algorithm                                               | 33   |

| Figure 3.2  | Architecture implemented on simulator for evaluation of           | 35   |

|             | locks, transactions and semaphores.                               |      |

| Figure 3.3  | Energy consumption by the use of locks, transactions and          | 37   |

| T' 0.4      | semaphores                                                        | 2.77 |

| Figure 3.4  | Cache miss rate by the use of locks, transactions and semaphores  | 37   |

| Figure 4.1  | Cache associativity: direct mapped and 2-way associative          | 41   |

|             | cache                                                             |      |

| Figure 4.2  | Algorithm for proposed SPM replacement policy                     | 43   |

| Figure 4.3  | Two level architecture implemented for SPM replacement            | 44   |

|             | policy evaluation                                                 |      |

| Figure 4.4  | Direct mapped: cache miss rate with SPM and without SPM           | 46   |

|             | using 6 benchmarks                                                |      |

| Figure 4.5  | Fully associative: cache miss rate with SPM and without      | 46 |

|-------------|--------------------------------------------------------------|----|

|             | SPM using 6 benchmarks                                       |    |

| Figure 4.6  | Cache miss rate for biquad benchmark for different           | 47 |

|             | associativity values                                         |    |

| Figure 4.7  | 2-way associative cache: cache miss rate using SPM and       | 47 |

|             | without using SPM using 6 benchmarks                         |    |

| Figure 4.8  | 4-way associative cache: cache miss rate using SPM and       | 48 |

|             | without using SPM using 6 benchmarks                         |    |

| Figure 4.9  | 8-way associative cache: cache miss rate using SPM and       | 48 |

|             | without using SPM using 6 benchmarks                         |    |

| Figure 4.10 | Cache miss rate for bubble sort with increasing number of    | 50 |

|             | elements in direct mapped cache.                             |    |

| Figure 4.11 | Cache miss rate for bubble sort with increasing number of    | 50 |

|             | elements in 2-way associative cache.                         |    |

| Figure 4.12 | Cache miss rate for bubble sort with increasing number of    | 51 |

|             | elements in 4-way associative cache                          |    |

| Figure 4.13 | Cache miss rate for bubble sort with increasing number of    | 51 |

|             | elements in 8-way associative cache                          |    |

| Figure 4.14 | Cache miss rate for bubble sort with increasing number of    | 52 |

|             | elements in fully associative cache                          |    |

| Figure 5.1  | Interleaved structure                                        | 58 |

| Figure 5.2  | An example of merge sort using the concept of interleaving   | 58 |

| Figure 5.3  | Modified merge sort, merge and insertion sort algorithms for | 61 |

|             | memory map simulator                                         |    |

| Figure 5.4  | DL1 (SPM) hit ratio for normal and interleaved merge sort    | 62 |

| Figure 5.5  | L2 cache hit ratio for normal and interleaved merge sort     | 63 |

| Figure 5.6  | SPM cache miss rate, replacement rate and write back rate    | 64 |

|             | using merge sort plain and also interleaved                  |    |

| Figure 5.7  | L2 cache miss rate, replacement rate and write back rate     | 64 |

|             | using merge sort plain and also interleaved                  |    |

| Figure 5.8  | Architecture used in sorting algorithm evaluation of Simple  | 65 |

|             | Scalar                                                       |    |

| Figure 5.9  | Memory map simulator design                                | 67 |

|-------------|------------------------------------------------------------|----|

| Figure 5.10 | Data flow graph of Memory Map simulator                    | 69 |

| Figure 5.11 | Snapshots of merge sort execution (non-interleaved and     | 70 |

|             | interleaved) on Memory Map simulator with 128 Byte block   |    |

|             | size                                                       |    |

| Figure 5.12 | Hit ratio of 2-set LRU and FIFO replacement policies using | 71 |

|             | merge sort interleaving                                    |    |

| Figure 5.13 | Hit ratio of 2-set LRU and FIFO replacement policies in    | 71 |

|             | merge sort without interleaved memory                      |    |

| Figure 5.14 | Snapshots of bubble sort execution (non-interleaved and    | 72 |

|             | interleaved) on Memory Map simulator with 32 Byte block    |    |

|             | size                                                       |    |

| Figure 5.15 | Hit ratio of 2-set LRU and FIFO replacement policies using | 73 |

|             | bubble sort                                                |    |

| Figure 5.16 | Snapshots of average calculation of 30 elements execution  | 73 |

|             | (non-interleaved and interleaved) on Memory Map simulator  |    |

|             | with 32 Byte block size                                    |    |

| Figure 5.17 | Hit ratio of 2-set LRU and FIFO replacement policies using | 74 |

|             | interleaved average                                        |    |

| Figure 5.18 | Hit ratio of 2-set LRU and FIFO replacement policies using | 74 |

|             | average plain.                                             |    |

| Figure 6.1  | Architecture of proposed tag based dual replacement policy | 78 |

| Figure 6.2  | Hit ratio of 32B, 64B and 128 B block size of LRU, FIFO    | 80 |

|             | and dual replacement policies                              |    |

| Figure 6.3  | Energy estimation (µJ) of 32B, 64B and 128 B block size of | 80 |

|             | LRU, FIFO and dual replacement policies                    |    |

| Figure 7.1  | Architecture of proposed tag based dual replacement policy | 86 |

|             | in SPM                                                     |    |

| Figure 7.2  | Cache miss rate for FIFO, LRU, random and dual             | 88 |

|             | replacement policies using and without using SPM           |    |

|             | implementing 6 benchmarks for direct mapped associative    |    |

|             | cache                                                      |    |

| Figure 7.3  | Cache miss rate for FIFO, LRU, random and dual               | 89  |

|-------------|--------------------------------------------------------------|-----|

|             | replacement policies using and without using SPM             |     |

|             | implementing 6 benchmarks for 2-way associative cache.       |     |

| Figure 7.4  | Cache miss rate for FIFO, LRU, random and dual               | 89  |

|             | replacement policies using and without using SPM             |     |

|             | implementing 6 benchmarks for 4-way associative cache        |     |

| Figure 7.5  | Cache miss rate for FIFO, LRU, random and dual               | 90  |

|             | replacement policies using and without using SPM             |     |

|             | implementing 6 benchmarks for 8-way associative cache.       |     |

| Figure 7.6  | Cache miss rate for FIFO, LRU, random and dual               | 90  |

|             | replacement policies using and without using SPM             |     |

|             | implementing 6 benchmarks for fully associative cache.       |     |

| Figure 8.1  | Execution cycles in FFT with Dragon, Berkeley, MESI and      | 97  |

|             | Valid directory cache coherence protocols                    |     |

| Figure 8.2  | Execution cycles in LU with Dragon, Berkeley, MESI and       | 98  |

|             | Valid directory cache coherence protocols                    |     |

| Figure 8.3  | Execution cycles in OCEAN with Dragon, Berkeley, MESI        | 99  |

|             | and Valid directory cache coherence protocols                |     |

| Figure 8.4  | Execution cycles in RADIX with Dragon, Berkeley, MESI        | 100 |

|             | and Valid directory cache coherence protocols                |     |

| Figure 8.5  | Ratio of execution times for proposed valid directory vs s/w | 101 |

|             | based cache coherence solution                               |     |

| Figure 9.1  | Fraction associative mapping explanation                     | 108 |

| Figure 9.2  | Analysis of energy conversion using different benchmarks     | 108 |

|             | for 2-set FIFO, 2-set LRU and fraction associative mapping   |     |

| Figure 9.3  | Analysis of access time using different benchmarks for 2-set | 109 |

|             | FIFO, 2-set LRU and fraction associative mapping             |     |

| Figure 10.1 | MPSoC Architecture                                           | 115 |

| Figure 10.2 | Single bus architecture in MPSoC                             | 116 |

| Figure 10.3 | Network architecture in MPSoC                                | 117 |

| Figure 10.4 | A 4 x 4 mesh topology                                        | 118 |

| Figure 10.5 | A 4 x 4 torus topology                                       | 119 |

| Figure 10.6  | A 4 x 4 BFT topology                                         | 120 |

|--------------|--------------------------------------------------------------|-----|

| Figure 10.7  | A 4 x 4 EBFT topology                                        | 121 |

| Figure 10.8  | Throughput vs network load for flit length=10 in dijkstra's  | 129 |

|              | algorithm using BFT, mesh, torus and EBFT topologies         |     |

| Figure 10.9  | Throughput vs network load for flit length=32 in dijkstra's  | 130 |

|              | algorithm using BFT, mesh, torus and EBFT topologies         |     |

| Figure 10.10 | Latency vs network load for flit length=10 in dijkstra's     | 132 |

|              | algorithm using BFT, mesh, torus and EBFT topologies         |     |

| Figure 10.11 | Latency vs network load for flit length=32 in dijkstra's     | 132 |

|              | algorithm using BFT, mesh, torus and EBFT topologies         |     |

| Figure 10.12 | Throughput vs network load for flit length=10 in distance    | 134 |

|              | vector algorithm using BFT, mesh, torus and EBFT             |     |

|              | topologies                                                   |     |

| Figure 10.13 | Throughput vs network load for flit length=32 in distance    | 135 |

|              | vector algorithm using BFT, mesh, torus and EBFT             |     |

|              | topologies                                                   |     |

| Figure 10.14 | Average packet delay vs network load for flit length=10 in   | 136 |

|              | distance vector algorithm using BFT, mesh, torus and EBFT    |     |

|              | topologies                                                   |     |

| Figure 10.15 | Average packet delay vs network load for flit length=32 in   | 136 |

|              | distance vector algorithm using BFT, mesh, torus and EBFT    |     |

|              | topologies                                                   |     |

| Figure 10.16 | Throughput with increase in network size (packet size = 10   | 137 |

|              | flits)                                                       |     |

| Figure 10.17 | Throughput with increase in network size (packet size = 32   | 138 |

|              | flits)                                                       |     |

| Figure 10.18 | Average latency with increase in network size (packet size = | 138 |

|              | 10 flits)                                                    |     |

| Figure 10.19 | Average latency with increase in network size (packet size = | 139 |

|              | 32 flits)                                                    |     |

#### CHAPTER 1

#### INTRODUCTION

An embedded system is an element of a complete device in itself which includes hardware as well as software. Embedded systems have major applications in lots of day today's appliances. Reduction in memory size is essential to achieve better performance. Embedded devices also often have different design constraints in comparison with general purpose computers. Some embedded system constraints are listed below:

- 1. Available system-memory

- 2. Available processor speed

- 3. Limited power dissipation

There are strict constraints on the embedded systems for small system size, low weight, low power consumption, good performance, high reliability and low cost. All these factors play a major role in the application of embedded systems which are going to be discussed below in detail [P. J. Koopman, 1989].

- Size and weight: Applications such as aircrafts and portable equipments have a severe weight limitation. Some applications also have size limitation. A typical embedded system can have a maximum size in hardly any cubic inches and maximum weight in few pounds only.

- Reliability: Military and automotive applications need extremely reliable operating conditions that can deal with vibration, shock, extreme heat and cold etc because in remote areas, system must be capable enough to survive without any repair service.

- 3. Cost: Applications like consumer electronics products have cost as a very important factor. In general, system complexity is directly proportional to the system cost. Hence, these systems must be designed with very less complexity.

- 4. Power and cooling: Power consumption of the system is also affected by the system complexity. High power consuming systems require heavy and huge power supply mechanism. Moreover, more the power consumed by the system,

- more the heat produced and hence increase in the requirement of cooling mechanism.

- 5. Performance: There are a number of applications requiring higher performance, such as voice translation, moving picture recognition, and others. In many multimedia embedded applications performance constraints are formulated as soft or hard real-time time constraints for a periodic task, such as frame decoding in a video player. Unlike as in general purpose computers, where performance is an important optimization criteria, embedded systems may not always benefit from increased performance beyond given real-time constraints. For example, for a video player application, the user satisfaction with the device will not improve if the player can decode 100 instead of 30 frames per second, since the video clips are typically encoded with the rate of no higher than 30 fps due to the limited ability of a human eye to distinguish between fast changing frames.

#### 1.2 Cache Memory Overview

Cache memory is like random access memory accessed by processor faster than accessing a RAM. When a processor requires some data for a process execution, it first checks the presence of data in the cache memory and if it finds the data there, it needs not to read data from larger memory i.e memory at next level in hierarchy which is more time-consuming.

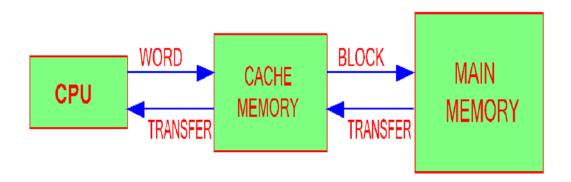

Figure 1.1: CPU organization

Cache is more close to processor as cache locates between normal main memory and CPU. The architecture of CPU is shown in fig. 1.1 [Rob Williams, 2006]. A word is transferred between CPU and cache memory while a block transfer takes place to and from main memory and cache memory.

#### 1.2.1 Unit of Transfer

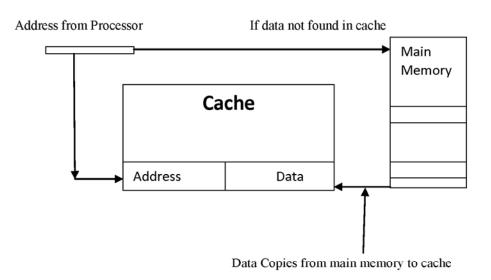

Figure 1.2 explains the concept of mapping a main memory address generated by the processor to cache memory [D. Tarnoff, 2006]. This mapping is used in case of reading and writing data from and to the cache memory. There are majorly three different types of mapping functions explained below.

Figure 1.2: A basic main memory to cache memory mapping scheme

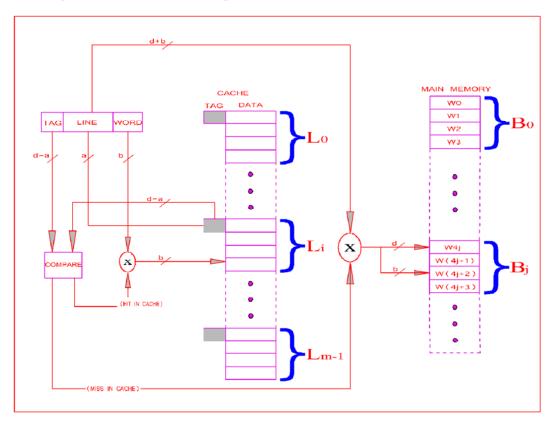

Direct mapping (fig. 1.3): [N.P.Jouppi, 1990] In case of direct mapping, each main memory block maps to only one cache line, hence it will always be found in the same place in memory by using formula given below [D. Tarnoff, 2006]:

$1 = b \mod m$  Where

1 = Number of mapped cache line.

b = Number of main memory block.

m = Number of cache lines

Advantages and disadvantages of direct mapping are [R. Williams, 2006]:

It is simple to understand.

It is economical

It has a permanent location for a given block

Figure 1.3: Direct mapping arrangement [M.D.Hill, 1988]

Ex. Main memory = $1MB = 2^{20}$

Cache memory=128KB= 2<sup>17</sup>

Block size= $16 B = 2^4$  Set size= 1block

No.of sets in cache= cache size / (block size \* set size) =  $2^{17}$  / ( $2^{4}$ \* 1) =  $2^{13}$

No. Of tag bits = 20 - 13 - 4 = 3

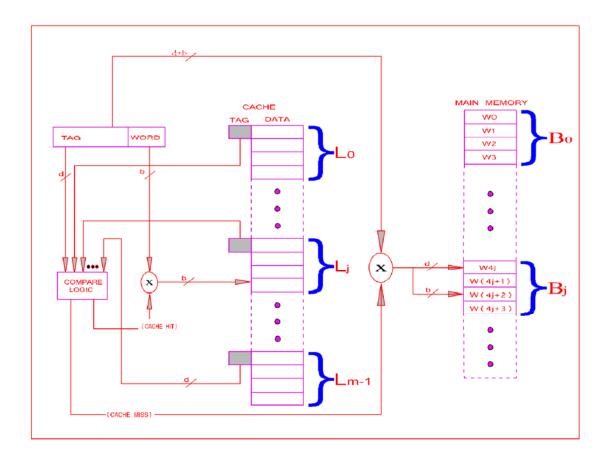

2. Fully associative mapping (fig. 1.4): In this mapping, a main memory block can be mapped to any cache block as whole memory is one set here [D. Tarnoff, 2006]. The size of tag is d bits and word size is b bits.

Figure 1.4: Fully associative mapping arrangement [M.D.Hill, 1988]

Ex. Main memory =256MB=

$$2^{28}$$

Cache memory=64KB=  $2^6$

Block size=32 B =  $2^5$

No. Of tag bits = 28 - 5 = 23

3. Set associative mapping (fig. 1.5): Cache is divided into m sets. N blocks/lines can be contained within each set. Such a cache memory is called n-way set associative. It is hybrid of direct and associative mapping [D. Tarnoff, 2006].

Number of lines in a cache =  $m \cdot n$

Size of tag = (d-b) bits

when n = 1, direct mapping

when m = 1, fully associative mapping

Ex. Main memory = $1MB = 2^{20}$

Cache memory=128KB= 2<sup>17</sup>

Block size= $16 B = 2^4$  Set size= 8blocks= $2^3$

No. of sets in cache= cache size / (set size \* block size) =  $2^{17}$  / ( $2^3 * 2^4$ ) =  $2^{10}$

No. Of tag bits = 20 - 10 - 4 = 6

A main memory block can map to any cache block in its specified set as shown in the fig. 1.5.

Figure 1.5: Sct associative mapping arrangement [M.D.Hill, 1988]

### 1.2.2 Locality of Reference [A.A.Jayya, 2005]

In programming, instructions and data are likely to cluster together (loops, subroutines etc.), this property is referred to locality of reference.

- Clusters will change in long duration.

- Clusters remain same in short duration [D. Tarnoff, 2006].

There are 3 types of locality of reference which can be exploited to keep more frequently referenced information into cache memory.

- Spatial locality: The tendency of a process to retrieve items whose addresses are close to one another is called spatial locality [M. Mano, 1989]. For example, operations on tables or arrays involve accesses of a certain clustered area in the address space.

- 2. Temporal locality: Memory items that are recently referenced are more likely to be referenced soon than those which have not been referenced for a longer time. Memory items (instructions or data) in a few localized areas of the memory (program or data structure) are more frequently referenced than other areas. (Ex: loops, functions, subroutines, arrays etc.)

- 3. Sequential locality: Execution of instructions follows a sequential order unless branch instructions create out of order executions.

# 1.2.3 Replacement Policy

The main objective of replacement policy is to locate a space in cache memory for a required main memory block. The replacement policy tells the slot to be swapped out to make space free for the new block [M.J. Murdocca, 2007]. Some of the most widely used replacement policies are:

- Belady's algorithm: The most efficient caching algorithm rejects the unwanted information for the longest duration in the future reference. This optimal choice is referred to as Belady's optimal algorithm or sometimes the clairvoyant algorithm. Since it is generally impossible to guess how far in the future this information will be needed, hence this is generally not possible to implement in practice.

- Random: In this policy, a victim block is randomly chosen and then discarded to

make space for new block. Due to its simplicity, it has been used in ARM

processors. It admits efficient stochastic simulation.

- FIFO (First-In First-Out): The easiest page-replacement algorithm is FIFO algorithm. As the name suggests, it keeps track of all the pages in memory by implementing a queue, by keeping the latest arrived page at the back, and the earlier arrived pages in front. As deletion in queue is done from front, so as the

memory page from the front is replaced to vacant room for the new block to be inserted at the end of the queue [Shenoy, 2008]. Although, it does not perform good in practical application, still it is cheap.

LRU (Least Recently Used): Least recently used discards the least recently used memory blocks first. When each block is used record is maintained by this algorithm which is an expensive job.

# 1.2.4 Cache Addressing Models [A. A. Jerraya, 2005]

There are two cache addressing models. One is physical address cache and another is virtual address cache. Both are discussed in detail below.

Physical address cache: When a cache is accessed with a physical memory address, it is called a physical address cache. Cache is indexed and tagged with physical address. Figure 1.6 describes the concept of physical addressing.

Figure 1.6: A unified cache accessed by physical address [Mark D. Hill, 1987]

# Different pros and cons are:

- There is no need to perform cache flushing.

- There are no aliasing problem

- It slows down accessing cache until MMU finishes translating the address.

Virtual address cache: When a cache is indexed or tagged with a virtual address, it is called virtual address cache. In this model, both cache and MMU translation can be done in parallel. Virtual addressing is shown in fig. 1.7.

Figure 1.7: A unified cache accessed by virtual address [Mark D. Hill, 1987]

Different pros and cons are:

- Enhanced efficiency to access cache faster.

- Cache aliasing

- Frequent cache flushing

# 1.2.5 Memory Capacity Planning

As only a fraction of all main memory blocks can be placed in cache memory (CM) at a time, a word needed by the CPU may or may not be found in cache memory.

Hit ratio, H: Probability for the CPU to find the needed information in cache memory.

$$Hit\ Ratio = \frac{No.of\ times\ referenced\ words\ are\ in\ cache}{Total\ Number\ of\ memory\ accesses}$$

Miss ratio, M: Probability of not finding the needed information in cache memory and main memory has to be accessed.

$$M = 1-H$$

Access frequency to Mi:

$$F_i = (1-H_1)(1-H_2)....(1-H_{i-1})H_i$$

Here H<sub>i</sub> corresponds to hit ratio at i<sup>th</sup> memory level.

Effective access time is defined as time taken to access data. [K.Hwang, 1993]

$$Effective \ access \ time = \frac{(No.of \ hits)(Time \ per \ hit) + (No.of \ misses)(Time \ per \ miss)}{Total \ number \ of \ memory \ accesses}$$

$T_{eff} = Sum (F_i * T_i)$  for all memory levels

Cost optimization:

$C_{total} = Sum (C_i * S_i)$  for all memory levels

Here C<sub>i</sub> represents cost of cache per bit and S<sub>i</sub> denotes the size of cache in bits at level i.

#### 1.3 Systems on Chip

A system on a chip is an integration of computer components like processor, memories, communication network etc on a single chip. Embedded systems are characteristic applications of SoC. The SoC and microcontroller both are of same degree. Normally, microcontrollers have RAM of capacity 100 KB with single-chip-systems, while SoC has more powerful processors proficient of running desktop versions of Windows and Linux, which require external memory chips and are also used with a range of external peripherals. System on a chip indicates a technical direction more than reality and hence

chip integration is increasing day by day to cut down manufacturing costs and to facilitate smaller systems.

# 1.4 Multiprocessor Systems on Chip

An MPSoC is a system on-chip, a VLSI system that incorporates most or all the components necessary for an application—that uses multiple programmable processors as system components. MPSoC's are widely used in networking, communications, signal processing and multimedia among other applications. MPSoC's embody an important and distinct branch of multiprocessors. They are not simply traditional multiprocessors shrunk to a single chip however they have been designed to satisfy the unique requirements of embedded applications. MPSoC's have been in production for much longer than multi core processors. In MPSoC's, each processor has its own cache memory with one or two levels, which is called local memory. In addition they have an independent private cache memory for each processor; there is a possibility that two or more cache memories may contain different versions of the same information at the same time. This is called cachememory coherence problem discussed in detail later in this chapter.

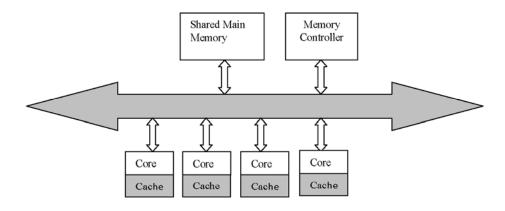

Figure 1.8: Architecture of multiprocessor system with shared memories [V. Gandhi, 2013]

Figure 1.8 shows the traditional view of architecture of shared-memory multiprocessor i.e. a collection of processors and memory connected by an interconnection network. This architecture is less complicated and hence preferred than others.

The architecture of an MPSoC system is a combination of three things: PE's, memory elements and a communication infrastructure for communication between both. While keeping processing in mind, MPSoC's are classified into two classes:

- Homogeneous: In a homogeneous system, all PE's in the system have the same architecture. The fact that all PE's have the same architecture facilitates task migration, as a result of there's no would like for translating the code of a given application to alternative design.