D/ Shout

## JAYPEE UNIVERSITY OF INFORMATION TECHNOLOGY, WAKNAGHAT TEST -3 EXAMINATION- JUNE 2016

## B.Tech VI Semester

COURSE CODE: 10B11EC612

MAX. MARKS: 35

COURSE NAME: VLSI TECHNOLOGY AND APPLICATIONS

**COURSE CREDITS: 04**

MAX. TIME 2 HRS

*Note:* All questions are compulsory.

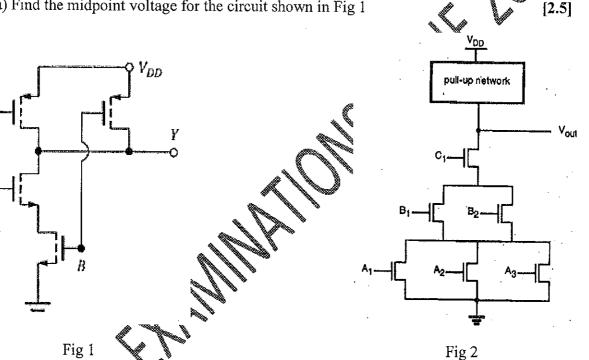

1. a) Find the midpoint voltage for the circuit shown in Fig 1

- b) A CMOS NOR gate is designed using nMOS with a value of  $k_n$  and pMOS by  $k_p$ . MOS aspect ratios are 6 and 8 respectively. Find the value of  $V_{\rm IH}$  in terms of  $V_{\rm out}$  for the case of simultaneous switching if  $V_{\rm DD} = 3.3 \, \text{V}$ ,  $V_{\rm Tn} = 0.65 \, \text{V}$ ,  $V_{\rm Tp} = -0.80 \, \text{V}$ ,  $k_n = 150 \, \mu \text{A/V}^2$ ,

- 2. Consider the circuit diagram given in Fig 2.

- a) Determine the logic function F. Find the equivalent nMOS inverter circuit for simultaneous switching of all input of Fig 2, assuming that  $(W/L)_n = 12$  for all *n*-mos transistor. [2]

- b) The inverter is biased at 5V. The threshold voltages are  $V_{TOD} = 1V$ ,  $V_{TOL} = 2V$ ,  $K_n' = 25\mu A/V^2$ ,  $\gamma = 0.4 V^{1/2}$ ,  $|2\phi_f| = 0.5 V$ . Design the inverter such that maximum power dissipation is 400  $\mu$ W for output voltage is 0.4V. Assume Pull up network as Saturated Load Inverter.

- 3. a) A p-channel transistor for which  $|V_{th}| = 1.2 \text{V}$  and  $|V_A| = 40 \text{V}$  operates in saturation with  $|V_{GS}| = 2 \text{V}$  and  $|V_{DS}| = 5 \text{V}$ , and  $i_D = 5 \text{mA}$ . Find the corresponding signed values for  $V_{SG}$ ,  $V_{SD}$ ,  $\lambda$ ,  $k_p$  (W/L). [0.5 + 0.5 + 0.5 + 1 = 2.5]

- b) A particular enhancement MOSFET for which  $V_{th} = 0.8$ V and  $k_n$ ` (W/L) = 0.1mA/V<sup>2</sup> is to be operated in the saturation region. If  $I_d$  is to be 0.2 mA, find the minimum required  $V_{DS}$ .

- c) For an *n*-mOS transistor for which  $V_{th} = 1V$ , operating with  $V_{GS}$  in the range of 1.25V to 5V, what is the largest value of  $V_{DS}$  for which the channel remains continuous? [1]

- 4. In the inverter circuit, what is meant by  $Z_{P.U.}$  and  $Z_{P.D.}$ ? What are pass transistors? Derive  $Z_{pu}$  to  $Z_{pd}$  ratio for an nMOS inverter driven through one or more series pass transistors.

[1+1+3=5]

5. Explain the different steps of fabrication of n - depletion type IGFET.

[5]

- 6. Consider the following parameters for n- channel enhancement type MOSFET having linearly graded junction profile. Substrate doping =  $3 \times 10^{12}$  cm<sup>-3</sup>, Source/Drain doping =  $1 \times 10^{19}$  cm<sup>-3</sup>, Sidewall (P+) doping =  $2 \times 10^{22}$  m<sup>-3</sup>, gate exide thickness = 40 nm, junction depth= 1.2  $\mu$ m, length of drain = 10  $\mu$ m, width = 5  $\mu$ m gate drain overlap length= 0.25  $\mu$ m,  $m_{sw}$  = 0.5. Both the source and drain diffusion regions are surrounded by P+ channel stop implant. If drain voltage changes from 2.5 V to 5  $\mu$  1 indedrain substrate diffusion capacitance. [5]

- 7. Draw the stick diagram of Sun Function of Full Adder using CMOS logic.

[2+3=5]