# DESIGN AND SIMULATION OF MEMBERSHIP FUNCTIONS FOR FUZZIFICATION MODULE OF FUZZY SYSTEM

Project Report submitted in partial fulfilment of the requirement for the degree of

#### **BACHELOR OF TECHNOLOGY**

IN

#### ELECTRONICS AND COMMUNICATION ENGINEERING

By

| Paras Goyal     | (121002)   |

|-----------------|------------|

| Sachin Arora    | (121023)   |

| Dalchand Sharma | n (121046) |

### UNDER THE GUIDANCE OF

Dr. Shruti Jain

JAYPEE UNIVERSITY OF INFORMATION TECHNOLOGY, WAKNAGHAT SOLAN – 173 234, HIMACHAL PRADESH INDIA June- 2016

## TABLE OF CONTENTS

| Chapter No. | Topics                                                | Page No. |

|-------------|-------------------------------------------------------|----------|

|             | Declaration by the scholar                            | iv       |

|             | Supervisor's certificate                              | v        |

|             | Acknowledgement                                       | vi       |

|             | List of acronyms and abbreviations                    | vii      |

|             | List of Figures                                       | viii - x |

|             | List of Tables                                        | xi - xii |

|             | Abstract                                              | xiii     |

| Chapter-1   | Introduction                                          | 1 - 8    |

|             | 1.1 Operational Amplifier                             | 3        |

|             | 1.2 Metal Oxide Semiconductor Field Effect Transistor | 5        |

|             | 1.3 Two Stage CMOS Operational Amplifier              | 7        |

| Chapter-2   | Existing Membership Functions                         | 9 – 16   |

|             | 2.1 Sigmoidal (S) – Membership Function               | 9        |

|             | 2.2 Antisigmoidal (Z) – Membership Function           | 11       |

|             | 2.3 Trapezoidal Membership Function                   | 13       |

|             | 2.4 Triangular Membership Function                    | 15       |

| Chapter-3   | <b>Proposed Membership Functions</b>                  | 17 – 25  |

|             | 3.1 Antisigmoidal or Z – Membership Function          | 17       |

|             | 3.2 Proposed Circuit of Gaussian Membership Function  | n 18     |

|           | 3.3 Proposed Circuit of Sigmoidal Membership Function | 21      |

|-----------|-------------------------------------------------------|---------|

|           | 3.4 Proposed Circuit of Antisigmoidal Membership      |         |

|           | Function                                              | 22      |

| Chapter-4 | MIN/MAX operators                                     | 26 - 43 |

|           | 4.1 MIN Circuit                                       | 26      |

|           | 4.1.1 Applications of MIN Circuit                     | 27      |

|           | 4.2 MAX Circuit                                       | 34      |

|           | 4.1.1 Applications of MAX Circuit                     | 36      |

| Chapter-5 | <b>Conclusion and Future Work</b>                     | 44      |

|           | List of Publications                                  | 45      |

|           | References                                            | 46 – 47 |

# **DECLARATION BY THE SCHOLAR**

I hereby declare that the work reported in the B-Tech thesis entitled "Design and Simulation of Membership Functions for Fuzzification Module of Fuzzy System" submitted at Jaypee University of Information Technology,Waknaghat, Solan, H.P. is an authentic record of my work carried out under the supervision of Dr. Shruti Jain. I have not submitted this work elsewhere for any other degree or diploma.

Jalen

Paras Goyal

Sachin Arora

Dalchand Sharma

Department of Electronics and Communication

Jaypee University of Information Technology, Waknaghat, Solan, H.P.

Date: 23/05/2016

# SUPERVISOR'S CERTIFICATE

This is to certify that the work reported in the B-Tech. thesis entitled "Design and Simulation of Membership Functions for Fuzzification Module of Fuzzy System", submitted by Paras Goyal, Sachin Arora and Dalchand Sharma at Jaypee University of Information Technology, Waknaghat, Solan, H.P. is a bonafide record of his / her original work carried out under my supervision. This work has not been submitted elsewhere for any other degree or diploma.

Name: Dr. Shruti Jain

Jaypee University of Information Technology, Waknaghat, Solan, H.P.

Date: 23/05/2016

# ACKNOWLEDGEMENT

It is our foremost duty to express our deep regards & gratitude to our Project Guide **Dr. Shruti Jain**, under whose guidance & supervision we are able to work on the project *"Design and Simulation of Membership Functions for Fuzzification Module of Fuzzy System"*. Any amount of gratitude towards our family and friends can never be enough for the constant support they have provided us with, we are totally indebted to them. At last it is him, to whom we owe everything, as without God's blessings this endeavours of ours would never have been a success.

# LIST OF ACRONYMS & ABBREVIATIONS

- 1. MOSFET Metal Oxide Field Effect Transistor (We have used PMOS-D)

- 2. PMOS-D P type Metal Oxide Field Effect Transistor of Depletion mode

- 3. Mbreak P-X PMOS-D in ORCAD

- 4. Vdc DC voltage source

- 5. OPAMP **Operational Amplifier**

- 6. ua741 OPAMP 741 with all the pins opened for connections

# LIST OF FIGURES

| Figure No.<br>No. | Caption                                                      | Page |

|-------------------|--------------------------------------------------------------|------|

| Figure 1.1        | Fuzzy System Model                                           | 2    |

| Figure 1.2        | Equivalent circuit diagram of an ideal operational amplifier | 4    |

| Figure 1.3        | Symbol of Depletion and Enhancement mode MOSFET              | б    |

| Figure 1.4        | Two stage CMOS operational amplifier                         | 8    |

| Figure 2.1        | Circuit of S-membership function using OP-AMP                | 10   |

| Figure 2.2        | Output corresponding to S-membership function circuit        | 10   |

| Figure 2.3        | Circuit of Z-membership function using OP-AMP                | 12   |

| Figure 2.4        | Output of the circuit of Z-membership function               | 12   |

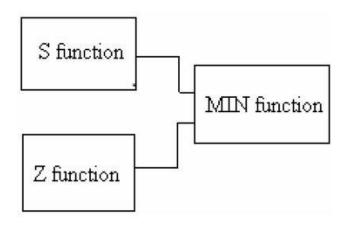

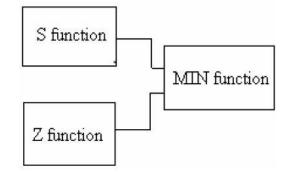

| Figure 2.5        | Block diagram showing how Trapezoidal function is made       | 14   |

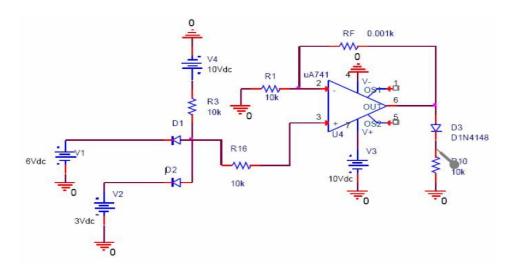

| Figure 2.6        | Circuit of MIN function                                      | 14   |

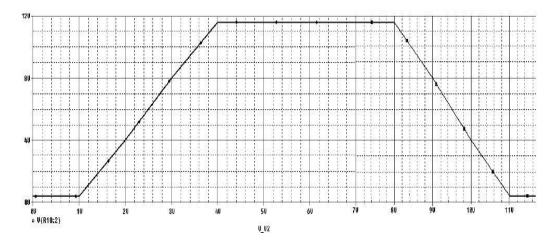

| Figure 2.7        | Output of the circuit of Trapezoidal function                | 14   |

| Figure 2.8        | Block diagram showing how Triangular function is made        | 15   |

| Figure 2.9        | Output of the circuit of MIN function                        | 16   |

| Figure 3.1        | Proposed circuit of Z – membership function                  | 17   |

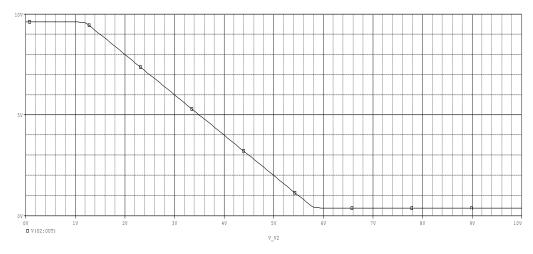

| Figure 3.2        | Output of the Proposed circuit of Z – membership function    | 17   |

| Figure 3.3        | Block diagram of proposed circuit                            | 18   |

| Figure 3.4        | Current Mirror circuit using PMOS                            | 19   |

| Figure 3.5        | Proposed circuit                                             | 20   |

| Figure 3.6        | Output corresponding to the proposed circuit                 | 20   |

| Figure 3.7  | S-membership function from Gaussian circuit                   |    |

|-------------|---------------------------------------------------------------|----|

|             | varying $V_1$ , $V_3$ , $V_4$ in circuit                      | 21 |

| Figure 3.8  | Z-membership function from Gaussian circuit                   |    |

|             | varying $V_1$ , $V_3$ , $V_4$ in circuit                      | 23 |

| Figure 4.1  | Circuit Diagram for MIN operator using op-amp                 | 27 |

| Figure 4.2  | Block Diagram showing MIN operator rule composition both      |    |

|             | Gaussian function                                             | 28 |

| Figure 4.3  | Output corresponding to the MIN circuit using both Gaussian   | 28 |

| Figure 4.4  | Block Diagram showing MIN operator rule composition using     |    |

|             | Sigmoidal & Gaussian function                                 | 29 |

| Figure 4.5  | Output corresponding to the MIN circuit using Sigmoidal &     |    |

|             | Gaussian function                                             | 29 |

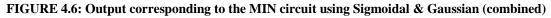

| Figure 4.6  | Output corresponding to the MIN circuit using Sigmoidal &     |    |

|             | Gaussian (combined)                                           | 30 |

| Figure 4.7  | Block Diagram showing MIN operator rule composition using     |    |

|             | Antisigmoidal & Gaussian function                             | 31 |

| Figure 4.8  | Output corresponding to the MIN circuit using Antisigmoidal & |    |

|             | Gaussian function                                             | 31 |

| Figure 4.9  | Output corresponding to the MIN circuit using Antisigmoidal & |    |

|             | Gaussian (combined)                                           | 32 |

|             |                                                               |    |

| Figure 4.10 | Block Diagram showing MIN operator rule composition using     |    |

|             | Z & S function                                                | 33 |

| Figure 4.11 | Output corresponding to the MIN circuit using Antisigmoidal &                                  |    |

|-------------|------------------------------------------------------------------------------------------------|----|

|             | Sigmoidal function                                                                             | 33 |

| Figure 4.12 | Circuit Diagram for MAX operator using op-amp                                                  | 35 |

| Figure 4.13 | Block Diagram showing MAX operator rule composition using                                      |    |

|             | both Gaussian function                                                                         | 36 |

| Figure 4.14 | Output corresponding to the MAX circuit using both Gaussian                                    |    |

|             | Function                                                                                       | 37 |

| Figure 4.15 | Block Diagram showing MAX operator rule composition using                                      |    |

|             | Sigmoidal & Gaussian function                                                                  | 38 |

| Figure 4.16 | Output corresponding to the MAX circuit using Sigmoidal &                                      |    |

|             | Gaussian function                                                                              | 39 |

| Figure 4.17 | Block Diagram showing MAX operator rule composition using<br>Antisigmoidal & Gaussian function | 40 |

| Figure 4.18 | Output corresponding to the MAX circuit using                                                  |    |

|             | Antisigmoidal & Gaussian function                                                              | 41 |

| Figure 4.19 | Output corresponding to the MAX circuit using                                                  |    |

|             | Antisigmoidal & Gaussian function (combined)                                                   | 41 |

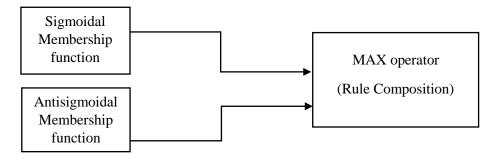

| Figure 4.20 | Block Diagram showing MAX operator rule composition using                                      |    |

|             | Antisigmoidal & Sigmoidal function                                                             | 42 |

| Figure 4.21 | Output corresponding to the MAX circuit using Z & S function                                   | 43 |

# LIST OF TABLES

| Table No. | Caption                                                                                             | Page No. |

|-----------|-----------------------------------------------------------------------------------------------------|----------|

| Table 2.1 | Electrical parameter values of Z – membership function circuit                                      | 13       |

| Table 3.1 | Electrical parameter values of proposed Z – membership function circuit                             | 18       |

| Table 3.2 | Electrical parameters of Proposed Circuit                                                           | 21       |

| Table 3.3 | S-membership function cases from proposed circuit varying $V_1$ , $V_3$ and $V_4$ in circuit        | 21 - 22  |

| Table 3.4 | Electrical parameters for cases of Table 3.3                                                        | 22       |

| Table 3.5 | Z-membership function cases from proposed circuit varying $V_1$ , $V_3$ and $V_4$ in circuit        | 23       |

| Table 3.6 | Electrical parameters for cases of Table 3.5                                                        | 23 - 24  |

| Table 3.7 | Table for variable $V_1$ and $V_3$ keeping $V_3=V_4$ in the circuit of Gaussian membership function | 24 - 25  |

| Table 3.8 | Electrical parameters for cases of Table 3.7                                                        | 25       |

| Table 4.1 | Electrical parameters of the Gaussian-Gaussian MIN<br>Composition                                   | 28       |

| Table 4.2 | Electrical parameters of the Sigmoidal-Gaussian MIN<br>Composition                                  | 30       |

| Table 4.3 | Electrical parameters of the Antisigmoidal-Gaussian MIN<br>Composition                              | 32       |

| Table 4.4 | Electrical parameters of the Sigmoidal-Antisigmoidal MIN<br>Composition                             | 34       |

| Table 4.5 | Electrical parameters of the Gaussian-Gaussian MAX<br>Composition                                   | 37       |

|           |                                                                                                     |          |

| Table 4.6 | Electrical parameters of the Sigmoidal-Gaussian MAX                 |    |

|-----------|---------------------------------------------------------------------|----|

|           | Composition                                                         | 39 |

| Table 4.7 | Electrical parameters of the Antisigmoidal-Gaussian MAX Composition | 42 |

| Table 4.8 | Electrical parameters of the Sigmoidal-Antisigmoidal MAX            |    |

|           | Composition                                                         | 43 |

# ABSTRACT

This report presents the proposed circuit for the designing of the Gaussian membership function using electronic devices like metal oxide semiconductor field effect transistor (MOSFET), operational amplifier (OPAMP) in ORCAD. Proposed circuit includes concepts of current mirror and current sink. In the proposed circuit we can also have Sigmoidal (S) and Antisigmoidal (Z) membership functions by varying various voltages. Moreover this report also includes the step of fuzzy model that is Rule Composition. In the rule composition process we have used the MIN and MAX operators and provided the Gaussian, Sigmoidal (S), Antisigmoidal (Z) combinations as an input.

# **INTRODUCTION**

Fuzzy systems is an alternative to traditional notions of set membership and logic, it has wide applications at the leading edge of Artificial Intelligence, Virtual reality, Automation of electronics devices like Air-Conditioner etc. It is a relatively new field, and as such leaves much room for development [21]. This report will present the basic concept of fuzzy logic, along with the concept of fuzzy system model, fuzzy membership functions both existed and proposed by us along with some basic idea of components used while making the fuzzy membership functions. Ultimately, it will be demonstrated that the use of fuzzy systems makes a viable addition to the field of electronics, and perhaps more generally to formal mathematics as a whole [4].

The Fuzzy logic is a powerful problem solver methodology with wide range of applications in industrial control, consumer electronics, management, medicine, expert system and information technology [2]. It provides a simple way to draw definite conclusions from imprecise or incomplete information. It provides the way of making the decision very close to the way the human beings thinks. It is a departure from classical two-valued sets and logic, that uses 'soft' linguistic (e.g., large, hot, tall) system variables and a continuous range of truth values in the interval [0, 1], rather than strict binary (true or false) decisions and assignments. The fuzzy logic based systems apply these methods to solve many types of 'real-world' problems, generally when the system is quite difficult to model [2].

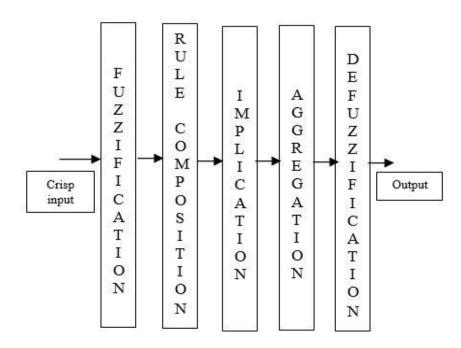

FIGURE 1.1: Fuzzy System Model

THERE ARE FIVE PARTS OF THE FUZZY SYSTEM AS SHOWN IN FIGURE 1 AND THEY ARE EXPLAINED BELOW STEP BY STEP.

<u>Step 1</u> *Fuzzification:* This is the first step in which we have to take the inputs and determine the degree to which they belong to each of the appropriate fuzzy sets via membership functions. In the fuzzy logic process, the input is always a crisp numerical value and the output is a fuzzy degree of membership in the qualifying linguistic set (always between the interval of 0 and 1).

<u>Step 2</u> *Rule composition*: After getting the fuzzified input from the previous step we come to know that the degree to which each part of the antecedent has been satisfied for each rule. If the antecedent of a given rule has more than one part, the fuzzy operator is applied to obtain one number that represents the result of the antecedent for that particular rule. Now this number will then be applied to the output function. The input to the fuzzy operator can be two or more membership values from fuzzified input variables. The output will going to be a singled truth value. There are different fuzzy operators: AND methods are supported: min (minimum) and prod (product), OR methods are also supported: max (maximum), and the probabilistic OR method probor.

<u>Step 3</u> *Implication*: Before applying this method, one should take care of the rule's weight. Every rule has a weight (a number between 0 and 1), which is applied to the number given by the antecedent. Generally, this weight is 1 and so it has no effect at all on the implication process. From time to time we may want to weight one rule relative to the others by changing its weight value to something other than 1.

<u>Step 4</u> *Aggregation*: Since we need to make a final decision based on the testing of all of the rules in an FIS, we must combine all the rules in order to make the final conclusion.

Inputs in aggregation process are the list of truncated output which we got by implying all the rules. The output of the aggregation process is one fuzzy set which is accomplished using different types of aggregation functions like max(maximum),probor (probabilistic OR) and sum (simply the sum of each rule's output set).

<u>Step 5</u> *Defuzzification*: The input for the defuzzification process is a fuzzy set (the aggregate output fuzzy set) and the output is a single number. As much as fuzziness helps the rule evaluation during the intermediate steps, the final desired output for each variable is generally a single number. However, the aggregate of a fuzzy set encompasses a range of output values and so must be defuzzified in order to resolve a single output value form the set. Perhaps the most popular defuzzification method is the centroid calculation, which returns the centre of area under the curve [2].

In this report, we will discuss regarding the designing and electronic implementation of fuzzy membership functions (Z (improved one), and Gaussian) using several electronic devices and simulating it with ORCAD software. But before that let us have a basic idea of some of the electronic components used while achieving the circuit of membership functions.

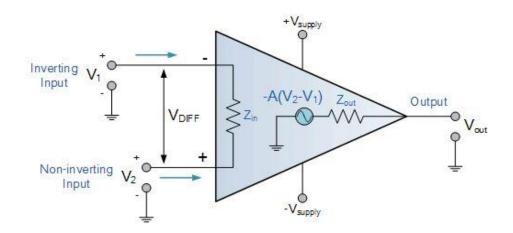

### 1.1 Operational Amplifier

An operational amplifier (OP-AMP) is a circuit that is generally used for signal amplification. It takes differential voltages present at its two terminals. And multiplies its difference by a gain factor and drives out the single ending output voltage. They are very effective in producing the large amount of gain or amplification which is having a vast

array of practical uses. OP-AMPS can be configured as per our requirements using the extra components like resistor, capacitor, inductor, diodes etc. [8].

An ideal OP-AMP has infinite open loop gain so as to get the maximum output, high input impedance due to which any source can drive it without any loss and zero output impedance so that there will be no change in output due to change in load current, which helps in maximum voltage gain, which is very useful when one is trying to amplify a small signal. The parameters like gain, input impedance, output impedance, bandwidth etc. are determined by using externally connected devices. It is used to amplify dc as well as ac input signals and was initially designed for performing the mathematical functions like addition, subtraction, multiplication, and integration [8].

#### FIGURE 1.2: Equivalent circuit diagram of an Ideal Operational Amplifier

Figure 1.2 shows the equivalent diagram of the OP-AMP where [8] -

- V<sub>1</sub> is Inverting Input Terminal

- V<sub>2</sub> is Non-Inverting Input Terminal

- A represents the infinite open loop gain

- $Z_{\rm in}$  is high input impedance

- Z<sub>out</sub>is zero output impedance

Various electrical parameters of op-amp [1] are:

- 1. *Differential input resistance*: Differential input resistance is the equivalent resistance that can be measured at either the inverting or non-inverting input terminal with the other terminal connected to ground.

- 2. *Output resistance*: Output resistance is the equivalent resistance that can be measured between the output terminal of the op-amp and the ground.

- 3. *Large signal voltage gain*: Since the op-amp difference voltage between two input terminals, the voltage gain of the amplifier is defined as the ratio of output voltage to differential input voltage. That is:

$$A = (V_{\rm o}/V_{\rm id})$$

Because output signal amplitude is much larger than the input signal, the voltage gain is commonly called large signal voltage gain.

4. *Common mode rejection ratio (CMRR)*: It is defined as the ratio of differential gain to common mode gain. A high CMRR helps to reject common mode signals such as noise successfully.

$CMRR = (A_d / A_{cm})$  $CMRR (dB) = 20 \log (A_d / A_{cm})$

5. *Slew rate (SR)*: It is defined as the maximum rate of change of output voltage per unit time and it is expressed in volts/microseconds.

$$SR = \max \left[ dV_{\rm o} / dt \right]$$

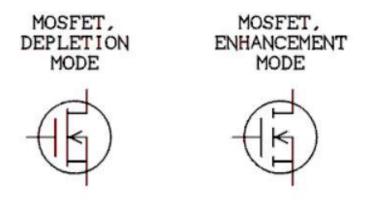

### 1.2 Metal Oxide Semiconductor Field Effect Transistor

The Metal Oxide Semiconductor Field Effect Transistor (MOSFET) is a voltage controlled field effect transistor that has a Metal Oxide Gate electrode which makes it electrically insulated from the main semiconductor n-channel or p-channel by a very thin layer of insulating material usually silicon dioxide, commonly known as glass [24].

The isolation of the controlling Gate makes the input resistance of the MOSFET very high and that would be in Mega ohms (M $\Omega$ ).

As the gate terminal is isolated from the main current carrying channel no current flows into the gate and MOSFET has a capability to acts like a voltage controlled resistor were the current flowing through the main channel between the drain and source is proportional to the input voltage. Like the FETs, the MOSFETs very high input resistance that can easily accumulate large amounts of static charge which make it very much sensitive [24].

MOSFETs are three terminal devices with a gate, drain and source and both P-channel (PMOS) and N-channel (NMOS) MOSFETs are available to us. The main difference which occurs is that the MOSFETs are available in two basic forms:

*Depletion Type* - The transistor requires the Gate-Source voltage ( $V_{GS}$ ), to bring the device in OFF state. The D-type MOSFET is equivalent to a "Normally Closed" switch. The depletion mode MOSFET comes in both the N channel device and P channel device and is more usually made as a discrete component, i.e. a single transistor rather than IC form [24].

FIGURE 1.3: Symbol of Depletion and Enhancement mode MOSFET

Therefore when the gate source voltage  $V_{GS}$  is zero, current (in the form of free electrons) can flow between source and drain. The gate is totally insulated from the channel by the layer of silicon dioxide. Now that a conducting channel is present the gate

does not need to cover the full width between source and drain. Because the gate is totally insulated from the rest of the transistor this device, like other IGFETs, has a very high input resistance.

*Enhancement Type* - The transistor requires a Gate-Source voltage,  $(V_{GS})$  to bring the device in the ON state. The E-type MOSFET is equivalent to a "Normally Open" switch. The gate has a voltage applied to it that makes it positive with respect to the source. This causes holes in the *P* type layer close to the silicon dioxide layer beneath the gate to be repelled down into the *P* type substrate, and at the same time this positive potential on the gate attracts free electrons from the surrounding substrate material. These free electrons form a thin layer of charge carriers beneath the gate electrode (they can't reach the gate because of the insulating silicon dioxide layer) bridging the gap between the heavily doped source and drain areas.

Any further increase in the gate voltage attracts more charge carriers into the inversion layer, so reducing its resistance, and increasing current flow between source and drain. Reducing the gate source voltage reduces current flow. When the power is switched off, the area beneath the gate reverts once again. Figure 1.3 above shows the symbol form of both the Depletion mode and the Enhancement mode [24].

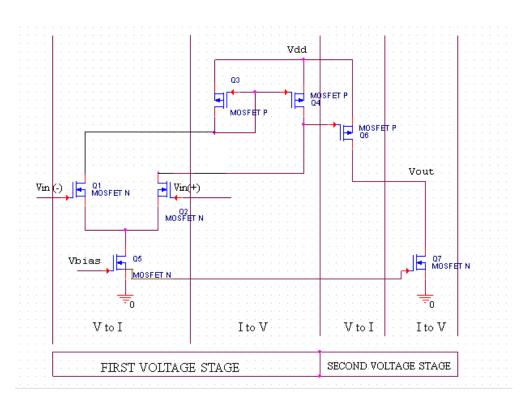

**1.3 Two stage CMOS operational amplifier**: Two-stage OP-AMP mainly consists of a cascade of voltage to current and current to voltage stages. The first stage consists of a differential amplifier converting the differential input voltage to differential currents. These differential currents are applied to a current mirror load recovering the differential voltage. The second stage consists of common source MOSFET (transconductance ground gate) converting the second stage input voltage to current. This transistor is loaded by a current sink load, which converts the current to voltage. Below figure 1.4 shows the circuit diagram of a 2 stage CMOS OP-AMP [13].

FIGURE 1.4: Two stage CMOS operational amplifier

By observing the Two stage CMOS operational amplifier circuit output we have made some conclusions and based on these conclusions we have proposed a new circuit for Gaussian membership function along with S and Z membership function.

We have used the PMOS-D is the circuit of Gaussian membership function which we will see below.

Later in this report we have discussed chapter 2 in which we have provided the existing membership functions regarding various membership functions ever existed and in chapter 3 we have provided the proposed membership functions

## **EXISTING MEMBERSHIP FUNCTIONS**

Earlier in the field of fuzzy logic system, several fuzzy membership functions (*S*-membership Function, Z-membership function, Triangular-membership Function, Trapezoidal-membership Function) were already implemented.

#### 2.1 Sigmoidal(S)-membership Function

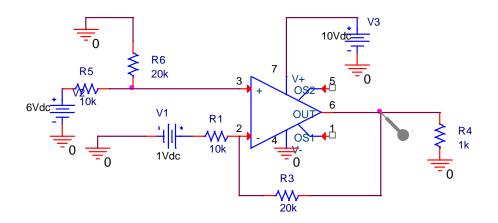

The Sigmoidal or S function can be generated by using the op-amp as a differential amplifier. The two inputs to the amplifier are  $V_x$  to the non-inverting terminal i.e. pin 3 of OP-AMP ua741 and  $V_c$  to the inverting terminal i.e. pin 2. The voltage  $V_x$  gives the variable crisp input voltage for which the fuzzified output is to be determined. The voltage  $V_c$  gives the constant input voltage up to which the output voltage will be zero. For voltages greater than  $V_c$ , the output voltage  $V_o$  will increase according to this slope of the *S* curve. The slope is given by the gain of the op-amp  $R_F/R_1$ . The output voltage is obtained from the formula [2]:

$$(dy/(x-c)) =$$

Slope

$dy = (x-c) (R_f/R_1)$

In terms of voltages,

$$V_{\rm o} = (V_{\rm x} - V_{\rm c})(R_{\rm f} / R_{\rm 1}) \tag{1}$$

The max output voltage that can be obtained has been set at 12 V because  $V_{CC} =$  12 V and therefore, the max output is  $+V_{sat} = 12$  V,  $V_{EE} = 0$  so all negative voltages will give 0 output. The S-membership function using op-amp is designed for gain  $(R_F / R_1)$  as 2, constant input voltage  $(V_c)$  as 1 V and the saturation voltage as 10 V. According to the formula given in equation (1), we get

$$10 = (V_x - 1)*2$$

So,  $V_x$  comes out to be 6 V [2].

Figure 4 illustrates the electronic implementation of S function. We have assumed gainas 2 so let's assume  $R_1$  as 10 K than  $R_F$  (for Figure 5:  $R_F = R_2$ ) is coming out to be 20 K. At the non-inverting terminal  $R_4$  is feedback resistance so its value is 20 K and  $R_3=R_1$ , i.e., 10 K.  $V_C$  is constant voltage which is at inverting terminal and given as 1 V,  $V_X$  is crisp voltage which is coming out to be 6 V by calculation. In this case saturation voltage is given as 10 V so pin 7 is connected to 10 V. Corresponding output of Figure 2.1 is shown in Figure 2.2 [2].

FIGURE 2.1: Circuit of S-membership function using OP-AMP

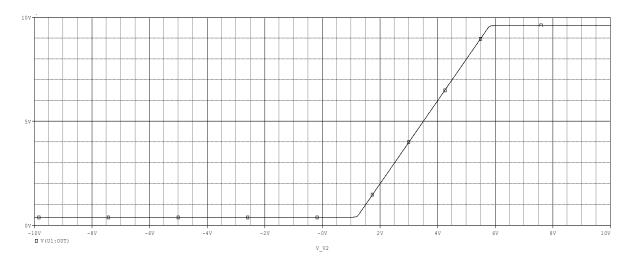

Figure 2.2 illustrates that slope starts with constant input voltage, i.e., 1 V and ends at the crisp input voltage which is 6 V (by calculation) with gain 2.

FIGURE 2.2: Output corresponding to S-membership function circuit

#### 2.2 Antisigmoidal(Z)-membership Function

The Antisigmoidal or Z-membership function generator can be designed by inverting the output of the circuit for the S function generator. The two voltage inputs are  $V_c$  and  $V_x$ ,  $V_x$ , is the variable crisp input voltage for which the fuzzified output is to be determined.  $V_c$  is the input voltage up to which the output voltage will be the maximum (12 V). For input voltage greater than  $V_c$ , the output voltage  $V_o$  decreases with increasing  $V_x$  according to the slope of the curve. This slope is again given by the gain  $R_F / R_1$  of the amplifier [2].

The output voltage is obtained from the formula:

$$(V_{\text{sat}} - dy)/(x-c) = \text{Slope}$$

$V_{\text{sat}} - V_o = (V_x - V_c) (R_F / R_1)$  (2)

The maximum output voltage that can be obtained is 12 V because  $V_{CC} = 12$  V. All negative voltages will be obtained as 0 at the output because  $V_{EE} = 0$  V. To change the slope of the curve, the gain  $R_F/R_1$  of the op-amp is to be changed. Also in order to change the voltage  $V_c$  up to which the output voltage remains maximum (12 V) voltage  $V_c$  is changed. If the gain remains same then the output voltage obtained for a certain input voltage  $V_x$  will be different from the output voltage obtained for a circuit with the same input voltage  $V_x$  and the gain but different  $V_c$ . If the same output voltages are desired for a given input voltage after changing  $V_c$ , then the gain (slope) of the circuit will have to be changed, accordingly.

The Z-membership function using op-amp is designed for gain  $(R_F / R_1)$  as 2.5, constant input voltage  $(V_c)$  as 3 V and the saturation voltage  $(V_o)$  as 10 V. According to the formula shown in equation (2), we get

$$10 = (V_{x} - 3)*2.5$$

$$4 = (V_{x} - 3)$$

$$V_{x} = 7V$$

So,  $V_x$  comes out to be 7*V*.

Now, the circuit shown below in Figure 2.3 is already prepared circuit of Z – membership function and Figure 2.4 is output along with its parameters value in Table 2.1. [2]

FIGURE 2.3: Circuit of Z – membership function using OP-AMP

FIGURE 2.4: Output of the circuit of Z – membership functions

| Electrical Parameter | Value      |

|----------------------|------------|

| Slew Rate (Rise)     | 1.99988    |

| Slew Rate (Fall)     | -1.99990   |

| Power dissipation    | -31.72329m |

### TABLE 2.1: Electrical parameter values of Z – membership function circuit

## 2.3 Trapezoidal-membership function

The trapezoidal function generator can be designed by minimising the output of the S and Z function generators.

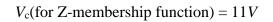

$V_x$  (for S-membership function) = 4V

$V_{\rm c}$  (for Z-membership function) = 11V

Thus, for voltages greater than  $V_X = 12 V$  the output will be zero. Now, if the outputs of the Z and S function generators are connected to the inputs of MIN function, i.e., similar to AND gate (connected two diodes in reverse order) the output will be of the shape of trapezoidal function [2].

Below figure 2.5 shows the block diagram showing how Trapezoidal function is made with the help of S, Z and MIN function.

The figure 2.6 below shows the circuit to obtain the Trapezoidal membership function using min circuit and its corresponding output in the figure 2.7 [2].

FIGURE 2.5: Block diagram showing how trapezoidal function is made

FIGURE 2.6: Circuit for MIN function

#### 2.4 Triangular-membership function

The triangular function generator can be designed by minimising the output of the S and Z function generators. The circuit used is the same as that used in the generator of trapezoidal function. But certain modifications have to been made regarding the inputs to the circuit [2].

In the S function generator,  $V_{c1}$ , below which the output voltages for all input voltages are 0 is taken as 3 V. For the input voltage  $V_x$  greater than 3 V, the output voltage will increase with increasing  $V_x$ , with a slope of  $R_F / R$  as 4. The voltage  $V_x$  at which the output voltage becomes maximum and remains so, even for increasing values of  $V_x$ . Hence,  $V_x$  comes out to be 6V.

In the Z function generator  $V_{c2}$ , given the input voltage below which the output voltage is always 12 V. For input voltage  $V_x$  greater than  $V_{c2}$ , the output voltage will decrease with increasing values of  $V_x$  according to the slope  $R_F / R$ . The values of  $V_x$  for which the output voltage becomes zero should be aligned with the 6V of S function. Hence the  $V_x$  comes out for it to be 10V [2].

Below figure 2.8 shows the block diagram showing how Triangular function is made with the help of S, Z and MIN function similar to the Trapezoidal function.

FIGURE 2.8: Block diagram showing how Triangular function is made

Below figure 2.9 shows the output corresponding to MIN function when  $V_x$  for S and  $V_c$  for Z membership function be 6 volts.

$$V_x$$

(for S-membership function) =  $4V$

## FIGURE 2.9: Output of the circuit of MIN function

So this is all about the background model. Now further we move to our proposed work which is illustrated in Chapter 3.

## **PROPOSED MEMBERSHIP FUNCTION**

Our main target is to design a circuit for Gaussian membership function and optimize the circuit of already made membership functions. So far we have optimized only the Z-membership function.

**3.1 Antisigmoidal or Z-membership Function**: We have made some changes in the existed Z-membership function by connecting directly inverter circuit to the S-membership function circuit. Now, below the circuit shown in Figure 3.1 is modified one and Figure 3.2 shows its output and Table 3.1 showing the parameters.

FIGURE 3.1: Proposed circuit of Z – membership function

| Electrical Parameter | Value (proposed) | Value (existing) |

|----------------------|------------------|------------------|

| Slew Rate (Rise)     | 1.99990          | 1.99988          |

| Slew Rate (Fall)     | -1.99989         | -1.99990         |

| Power dissipation    | -79.18455m       | -31.72329m       |

TABLE 3.1: Electrical parameter values of proposed Z – membership function circuit

Now above we can note that the difference in power dissipation is quite large. Hence, we can conclude that the *modified circuit is far better than the previous one*.

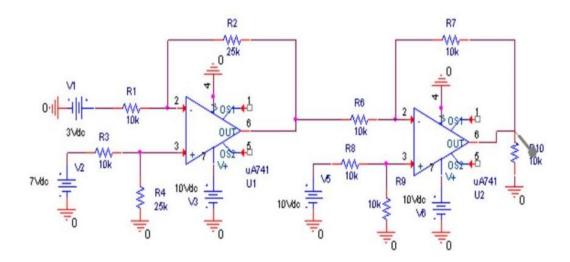

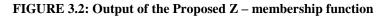

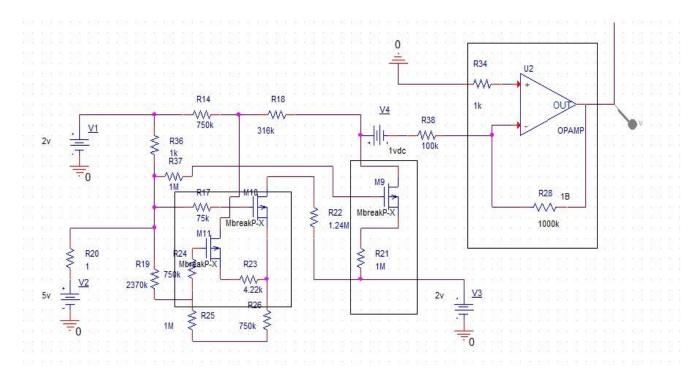

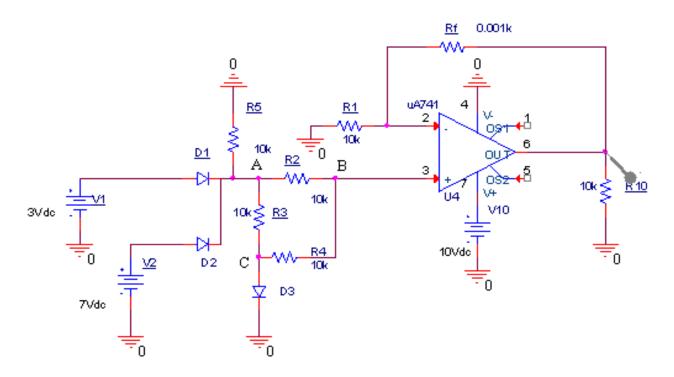

**3.2 Proposed circuit of Gaussian Membership Function**: We have designed the Gaussian – membership function circuit using two MOSFET  $M_1$  and  $M_2$  as current mirror circuit and  $M_3$  MOSFET forms current sink circuit and further we connected the OPAMP inverter circuit to invert the output of sink circuit and hence increase the gain so as to improve the amplitude.

We have divided the Gaussian membership function circuit into 3 parts as shown in figure 3.3.

FIGURE 3.3: Block diagram of proposed circuit

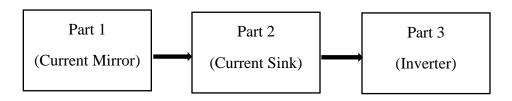

Part I: **Current Mirror**: The current mirror uses the principle that if gate - source potentials of two identical MOS transistors are equal, channel currents should be equal. Figure 3.4 shows the current mirror circuit using PMOS similar to which we have used in our proposed circuit.

#### FIGURE 3.4: Current Mirror circuit using PMOS

The conditions for the circuit to be mirror circuit are as follows:

- I)  $V_{gs(M1)} = V_{gs(M2)}$

- II) The gate terminal of both PMOS are to be connected

- III) The source terminals are to be connected

- IV) Drain current of both the PMOS are to be equal  $(I_{D1} = I_{D2})$

Part II: **Current Sink**: It is a two terminal device whose current is always independent of the voltage across its terminals. Current flows from positive node, through sink, to the negative node. Typically negative node is at  $V_{ss}$ . Gate voltage is applied to create the desired value of current accordingly. There is a threshold voltage  $V_{min}$  which is required for the current sink to start. In it we connected the drain of  $M_3$  to  $V_1$  and source to the circuit of current mirror.

Part III: **Inverter Circuit**: We have implemented the OPAMP Inverter circuit so as to get the inverted output of from the sink circuit along with increased gain so as to increase the amplitude

FIGURE 3.5: Proposed Circuit

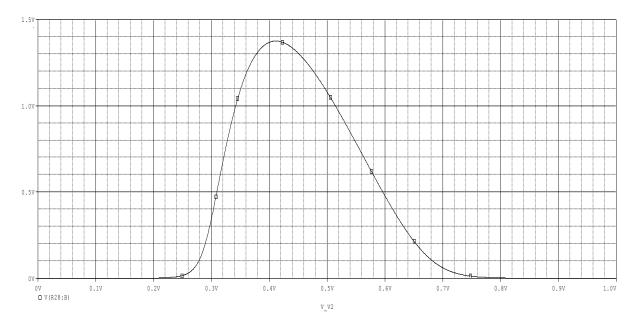

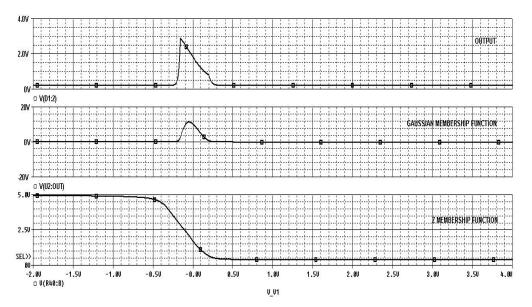

Figure 3.5 shows the proposed circuit to form Gaussian as well as S and Z membership function. Figure 3.6 below shows the output corresponding to the proposed circuit to form the Gaussian function and table 3.2 shows its electrical parameters.

FIGURE 3.6: Output corresponding to the proposed circuit

| Electrical Parameter | Value      |

|----------------------|------------|

| Power Dissipation    | -70.46493m |

| Slew Rate (Fall)     | -2.58573m  |

#### TABLE 3.2: Electrical parameters of the proposed circuit

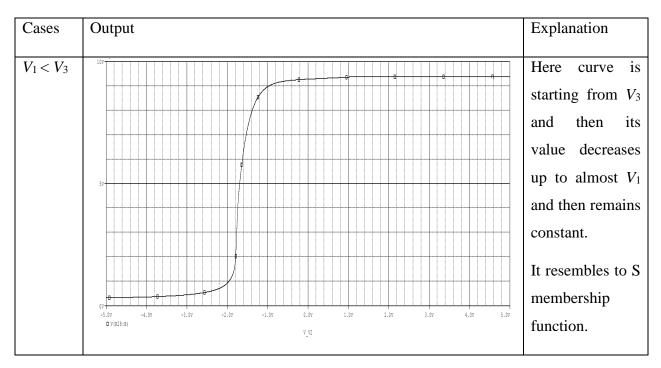

- **3.3 Proposed Circuit of Sigmoidal-membership function**: To achieve Sigmoidal or Smembership function from the proposed circuit we have following conditions-

- $V_3 > V_4$

- $V_3 = V_4 > V_1$

Table 3.3 shows the output of S-membership function for various cases obtained from proposed circuit satisfying the above condition and further Table 3.4 shows the electrical parameters for S-membership function circuit from proposed circuit.

| CASES                   | OUTPUT | EXPLANATION                                                    |

|-------------------------|--------|----------------------------------------------------------------|

| $V_1 = V_3 > V_4$       |        | Output voltage start                                           |

| $V_1 = V_4 < V_3$       |        | decreasing from $V_3$ to $V_4$ or $V_1$ and then further it is |

| $V_4 = V_3 > V_1$       |        | inverted and amplified using                                   |

| $V_3 = V_1 > V_4$       |        | op-amp inverter circuit in order to achieve S-                 |

| $V_{3} > V_{4} > V_{1}$ |        | membership function.                                           |

| $V_{3} > V_{1} > V_{4}$ |        |                                                                |

| $V_1 > V_3 > V_4$       |        |                                                                |

| $V_1 < V_3 > V_4$       |        |                                                                |

| $V_{3} > V_{4} < V_{1}$ |        |                                                                |

| $V_4 > V_1 < V_3$ and |  |

|-----------------------|--|

| $V_{3} > V_{4}$       |  |

|                       |  |

| Cases                   | Slew Rate | Power Dissipation |

|-------------------------|-----------|-------------------|

|                         | (SR-Rise) |                   |

| $V_1 = V_3 > V_4$       | 52.43366  | -644.37891u       |

| $V_1 = V_4 < V_3$       | 53.68333  | -770.47230u       |

| $V_4 = V_3 > V_1$       | 55.75744  | -7.04819m         |

| $V_3 = V_1 > V_4$       | 52.43360  | -644.37891u       |

| $V_{3} > V_{4} > V_{1}$ | 50.57349  | -769.29451u       |

| $V_{3} > V_{1} > V_{4}$ | 51.84653  | -709.83200u       |

| $V_1 > V_3 > V_4$       | 52.36998  | -713.58430u       |

| $V_1 < V_3 > V_4$       | 55.76450  | -729.47230u       |

| $V_{3} > V_{4} < V_{1}$ | 50.24681  | -6.76477m         |

#### TABLE3.4: Electrical parameters for cases of Table 3.3

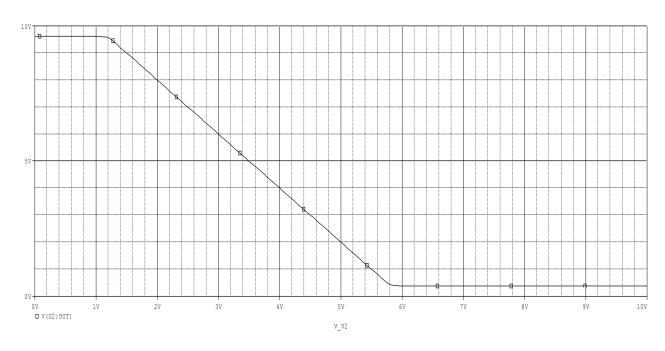

- **3.4 Proposed Circuit of Antisigmoidal or Z-membership function**: To achieve Antisigmoidal or Z-membership function from the proposed circuit we have following conditions-

- $V_4 > V_3$

- $V_3 = V_4 < V_1$

Table 3.5 shows the output of Z-membership function for various cases obtained from proposed circuit satisfying the above condition and further Table 3.6 shows the electrical parameters for Z-membership function circuit from proposed circuit.

| CASES                 | OUTPUT                                     | EXPLANATION                       |

|-----------------------|--------------------------------------------|-----------------------------------|

| $V_1 = V_3 < V_4$     |                                            | Output voltage start              |

| $V_1 = V_4 > V_3$     |                                            | increasing from $V_3$ to $V_4$ or |

|                       |                                            | $V_1$ and then further it is      |

| $V_4 = V_3 < V_1$     | 87                                         | inverted and amplified            |

| $V_3 = V_1 < V_4$     |                                            | using op-amp inverter             |

|                       |                                            | circuit in order to achieve       |

| $V_4 > V_3 > V_1$     |                                            | Z-membership function.            |

| $V_4 > V_1 > V_3$     |                                            |                                   |

| $V_1 > V_4 > V_3$     |                                            |                                   |

|                       |                                            |                                   |

| $V_4 < V_1 > V_3$     |                                            |                                   |

| $V_3 < V_4 > V_1$     | -100 (221:3)<br>107 (221:3)<br>107 (221:3) |                                   |

| $V_4$ > $V_1$ < $V_3$ |                                            |                                   |

| and $V_3 < V_4$       |                                            |                                   |

|                       |                                            |                                   |

TABLE 3.5: Z-membership function cases from proposed circuit varying  $V_1$ ,  $V_3$ , and  $V_4$  in circuit

| Cases             | Slew Rate<br>(SR-Fall) | Power<br>Dissipation |

|-------------------|------------------------|----------------------|

| $V_1 = V_3 < V_4$ | -8.97746               | -7.04819m            |

| $V_1 = V_4 > V_3$ | -7.59133               | -7.70472m            |

| $V_4 = V_3 < V_1$ | -8.77746               | -7.04819m            |

|                   |          | 1         |

|-------------------|----------|-----------|

| $V_3 = V_1 < V_4$ | -7.81590 | -6.44378m |

|                   |          |           |

| $V_4 > V_3 > V_1$ | -7.57537 | -7.69251m |

| $V_4 > V_1 > V_3$ | -6.14632 | -7.09823m |

| $V_1 > V_4 > V_3$ | -6.14369 | -7.15847m |

| $V_4 < V_1 > V_3$ | -8.57196 | -7.29220m |

| $V_3 < V_4 > V_1$ | -7.29341 | -6.76591m |

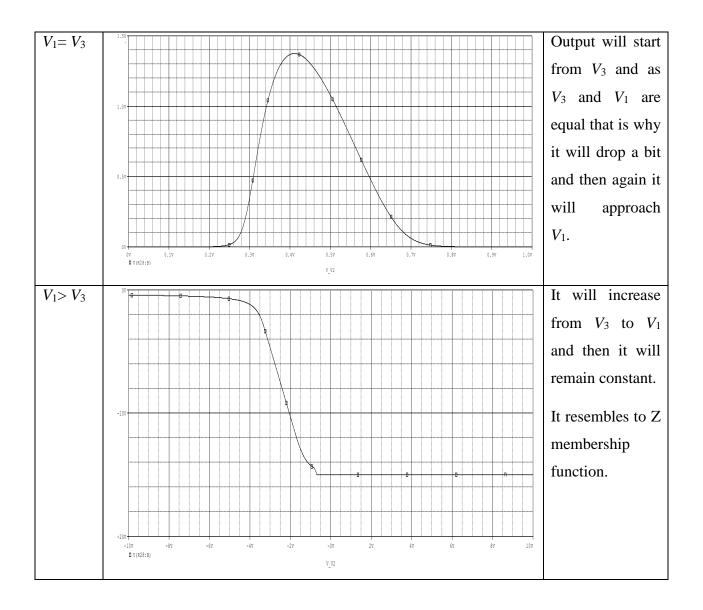

TABLE 3.7: Table for variable  $V_1$  and  $V_3$  keeping  $V_3 = V_4$  in the proposed circuit

TABLE3.8:

Electrical Parameters for Table 3.7

| Cases       | Slew Rate          | Power Dissipation |

|-------------|--------------------|-------------------|

| $V_1 < V_3$ | 55.75744 (SR-Rise) | -7.04716m         |

| $V_1 = V_3$ | -7.70833u(SR-Fall) | -7.704723m        |

| $V_1 > V_3$ | -8.97746           | -7.04819m         |

### **MIN/MAX OPERATORS**

As per the fuzzy system model, now the step comes after the *fuzzification* is *Rule Composition*. Once the inputs have been fuzzified, we know the degree to which each part of the antecedent has been satisfied for each rule. If the antecedent of a given rule has more than one part, the fuzzy operator is applied to obtain one number that represents the result of the antecedent for that rule. This number will then be applied to the output function. The input to the fuzzy operator is two or more membership values from fuzzified input variables. The output is a single truth value.

There are different fuzzy operators: AND methods are supported: min (minimum) and prod (product), OR methods are also supported: max (maximum), and the probabilistic OR method probor.

As this section uses the MAX & MIN circuits to perform the rule composition. The electronic implementation of these circuits is essential as these are the building blocks of Fuzzy System.

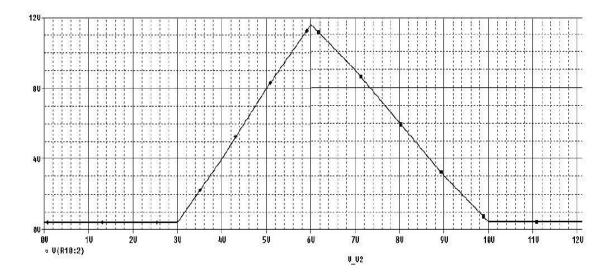

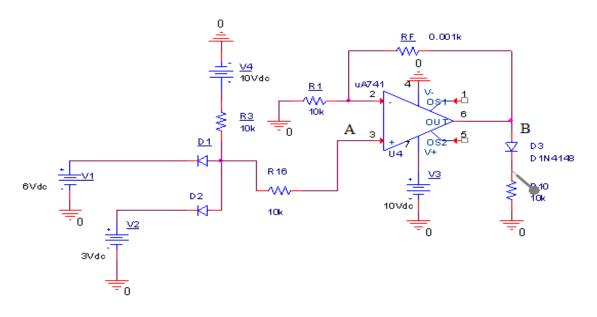

**4.1** *MIN circuit*: The MIN circuit can be realized by using diode in AND logic configuration which was given to the non-inverting terminal of an op-amp.

Let  $V_1 \& V_2$  be the two voltage inputs to the diodes  $D_1 \& D_2$  resp. The voltage at node A is the MIN of two inputs voltages  $V_1 \& V_2$  (AND logic). If  $V_1 < V_2$ , then  $V_1$  will appear at output i.e. node A otherwise  $V_2$  will appear. The actual voltage at node A is  $V_1 + V_\gamma$  where  $V_\gamma$  is the biased voltage of the diode.  $V_A$  is the input to the non-inverting terminal of the opmap. The input at non- inverting terminal should be equal to output so we have assumed the gain as 1 i.e. the output of op-amp at node B is  $V_1 + V_\gamma$ . To get output as  $V_1$ , diode  $D_3$  is an attached at the output with resistance  $R_{\rm L}$  in series with that. The final output is taken across load  $R_{\rm L}$  so that  $V_{\rm O} = V_{\rm O} - V_{\rm D3} = V_{\rm A}$ -  $V_{\gamma} = V_{\rm 1} + V_{\gamma} - V_{\gamma} = V_{\rm O}$ .

FIGURE4.1: Circuit Diagram for MIN operator using op-amp

Let us assume  $V_2 = 3$  volts and  $V_1 = 6$  volts, then output  $V_0 = MIN(6, 3) = 3$  volts shown in Fig 4.1.

In this report, we are trying to show the Gaussian-Gaussian composition, Sigmoidal (S)-Gaussian composition, Antisigmoidal (Z)-Gaussian composition, Sigmoidal (S)-Antisigmoidal (Z) composition, using both MIN and MAX operators.

#### 4.1.1 Application of MIN circuit

We have provided the several type of membership functions to max operator so as to achieve the rule composition.

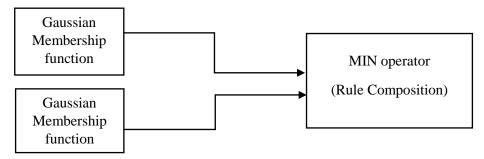

#### 1. Gaussian-Gaussian composition

We have passed the two membership functions both being Gaussian to MIN circuit as shown below in the block diagram fig. 4.2 and hence we got the output as per rule composition shown in fig. 4.3. Inputs are also shown in the same figure.

FIGURE 4.2: Block Diagram showing MIN operator rule composition both Gaussian function

Figure 4.3 explains the Gaussian inputs V (3) and V (4) and output at V (37), These inputs are fed up to MIN circuit and thus we get the output, output is also quite similar to Gaussian, Output curve initially follows input V (3) and then it follows input V (4).

FIGURE 4.3: Output corresponding to the MIN circuit using both Gaussian

Here with the application of above graphs we have calculated the parameters like Power dissipation and Slew rate rise or fall.

| Electrical Parameters | Value      |

|-----------------------|------------|

| Power Dissipation     | -31.52822u |

| Slew Rate (Rise)      | 2.20157u   |

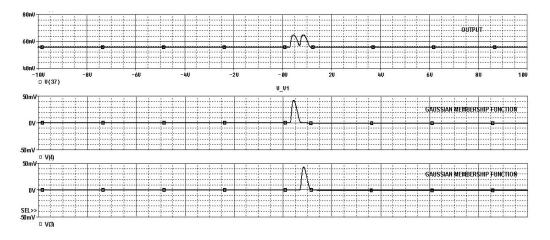

#### 2. Sigmoidal-Gaussian Composition (using MIN operator)

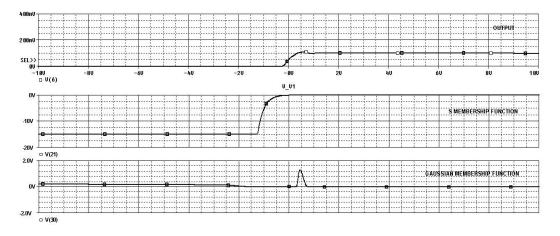

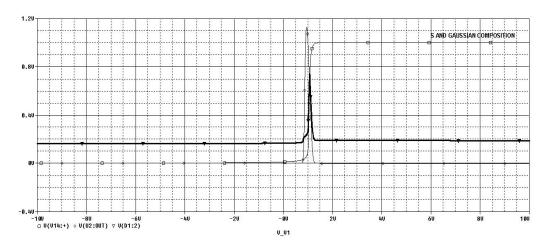

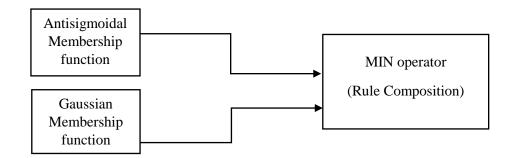

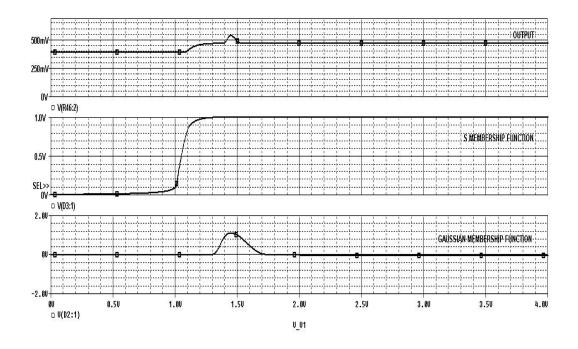

We have passed the two membership functions Sigmoidal and Gaussian to MIN circuit as shown in the fig. 4.4 and hence we got the output as per rule composition shown in fig. 4.5. Inputs are also shown in the same figure. Fig. 4.6 showing combined figure where output is highlighted.

FIGURE 4.4: Block Diagram showing MIN operator rule composition using Sigmoidal & Gaussian function

We have inputs at V (21) and V (30). At V (21) we are providing S-membership function as an input and at V (30) we are providing Gaussian membership function.

Output (V\_V1) initially follows S membership function and then Gaussian membership function. This is how we get the output which is shown in Fig 4.5

Here with the application of above graphs we have calculated the parameters like Power dissipation and Slew rate rise or fall. Here power dissipation is coming out to be negative which shows that work is done by charges.

TABLE 4.2:

Electrical parameters of the Sigmoidal-Gaussian MIN Composition

| Electrical Parameters | Value      |

|-----------------------|------------|

| Power Dissipation     | -61.79406u |

| Slew Rate (Rise)      | 7.7458u    |

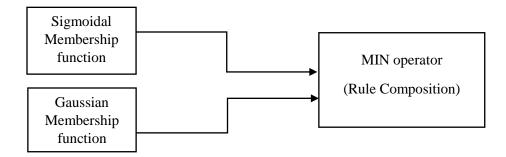

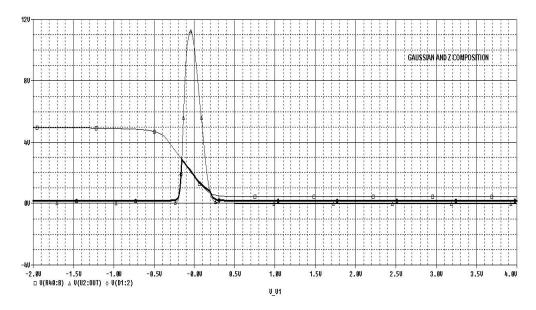

#### 3. Antisigmoidal-Gaussian composition (using MIN operator)

We have passed the two membership functions Antisigmoidal and Gaussian to MIN circuit as shown below in the block diagram fig. 4.7 and hence we got the output as per rule composition shown in fig. 4.8. Inputs are also shown in the same figure. Fig. 4.9 showing combined figure where output is highlighted.

FIGURE 4.7: Block Diagram showing MIN operator rule composition using Antisigmoidal & Gaussian function

In order to achieve the following output we fed Z-membership function at V (R48) and Gaussian membership function at V (U2) of MIN circuit. Output (VD1:2) initially follows the Gaussian membership function and then it follows Z-membership function. Because initially Gaussian membership function has lower value of voltage.

FIGURE 4.8: Output corresponding to the MIN circuit using Antisigmoidal & Gaussian function

FIGURE 4.9: Output corresponding to the MIN circuit using Antisigmoidal & Gaussian (combined)

Here with the application of above graphs we have calculated the parameters like Power dissipation and Slew rate rise or fall. Here power dissipation is coming out to be negative which shows that work is done by charges. And slew rate is also positive because it is taken in the case of rise.

| <b>Electrical Parameters</b> | Value      |

|------------------------------|------------|

| Power Dissipation            | -64.79851u |

| Slew Rate (Rise)             | 6.69536u   |

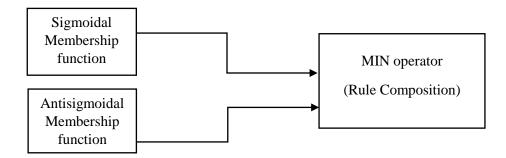

#### 4. S-Z composition (using MIN operator)

We have passed the two membership functions Antisigmoidal and Sigmoidal to MIN circuit as shown below in the block diagram fig. 4.10 and hence we got the output as per rule composition shown in fig. 4.11. Inputs are also shown in the same figure.

FIGURE 4.10: Block Diagram showing MIN operator rule composition using Z & S function

Here we have provided inputs S and Z respectively at V (14) and V(U2). S membership function has voltage range varying from 1V to 2V and z membership function from 4V to 10V.

FIGURE 4.11: Output corresponding to the MIN circuit using Antisigmoidal & Sigmoidal function

Here with the application of above graphs we have calculated the parameters like Power dissipation and Slew rate rise or fall. Here power dissipation is coming out to be negative which shows that work is done by charges. And slew rate is also positive because it is taken in the case of rise.

| Electrical Parameters | Value      |

|-----------------------|------------|

| Power Dissipation     | -62.89506u |

| Slew Rate (Rise)      | 7.68236    |

TABLE 4.4:

Electrical parameters of the Antisigmoidal-Sigmoidal MIN Composition

**4.2** *MAX circuit*: A two input MAX circuit can be realized by using the OR circuit output to the non-inverting terminal of an op-amp.

Let  $V_1$  and  $V_2$  the two voltages to the diodes  $D_1$  &  $D_2$  respectively. If  $V_1 > V_2$ , then the diode  $D_1$  will be more forward biased and voltage  $V_A = V_1 - V_\gamma$  will appear at node A, where  $V_\gamma$  is the biased voltage of diode  $D_1$ .

In order that the voltage input at node B,  $V_B$ , to the non-inverting terminal is equal to the  $V_1$ , a diode  $D_3$ , similar to diodes  $D_1$  and  $D_2$  is connected in parallel, across node A, so that the forward bias voltage (cut-in voltage,  $V_{\gamma}$ ) developed across  $D_3$  is added at node B to the output from the diode logic OR gate.

As a result, the op-amp effectively behaves as an adder circuit, with a gain of 1, in which the voltages  $V_A$  and  $V_\gamma$  are added and the output  $V_1$  is obtained, which is the maximum of the two voltages  $V_1$  and  $V_2$ .

For  $V_1 > V_2$

Voltage at node *A*,  $V_A = V_1 - V_\gamma$

Voltage developed across diode  $D_3$  at node C,  $V_C = V_{\gamma}$

Using the superposition theorem at node B, The voltage at node B, due to  $V_A$ , when  $V_C = 0$  is given by

$$V_{\rm BA} = (V_{\rm A}/R + R)^* R = V_{\rm A}/2 \tag{1}$$

FIGURE4.12: Circuit Diagram for MAX operator using op-amp

The voltage at node *B*, due to  $V_{\rm C}$ , when  $V_{\rm A} = 0$  is given by

$$V_{\rm BC} = (V_{\rm C}/R + R)^* R = V_{\rm C}/2 \tag{2}$$

Therefore,

$$V_{\rm B} = V_{\rm BA} + V_{\rm BC} = (V_{\rm A} + V_{\rm C})/2$$

(3)

Now, the output of the op-amp is given by

$$V_{\rm O} = (1 + R_{\rm F}/R_1)^* (V_{\rm A} + V_{\rm C})/2$$

(4)

Where  $(1 + R_F/R_1)$  is the gain of the non-inverting amplifier

For  $R_{\rm F} = R_1$

$$V_{\rm O} = 2* (V_{\rm A} + V_{\rm C})/2$$

$$V_{\rm O} = V_{\rm A} + V_{\rm C} \tag{5}$$

$$V_0 = V_1 \tag{6}$$

Thus, the output  $V_0$  of the op-amp is equal to the MAX of the two voltages  $V_1$  and  $V_2$ .

Now let us assume that  $V_2 = 7$  volts and  $V_1 = 3$ volts, then the circuit shown in Fig 4 will give us  $V_0 = Max(7, 3) = 7$  volts

#### **4.2.1** Application of MAX circuit:

We have provided the several type of membership functions to max operator so as to achieve the rule composition.

#### 1. Gaussian-Gaussian composition (using MAX operator)

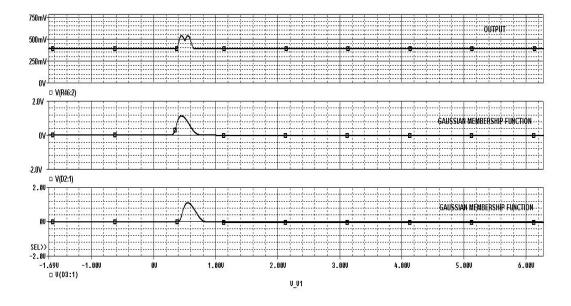

We have passed the two membership functions both being Gaussian to MAX circuit as shown below in the block diagram fig. 4.13 and hence we got the output as per composition shown in fig. 4.14. Inputs are also shown in the same figure.

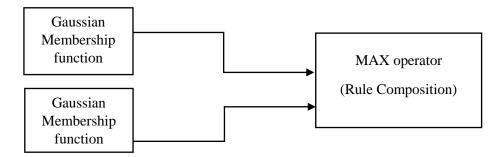

FIGURE 4.13: Block Diagram showing MAX operator rule composition using both Gaussian function

As it can be seen from output we have Gaussian inputs V(D2) and V (D3) and output at

V (R46), these inputs are fed up to MAX circuit and thus we get the output, output is also quite similar to Gaussian, Output curve initially follows input V (D2) and then it follows input V (D3).

FIGURE 4.14: Output corresponding to the MAX circuit using both Gaussian function

Here with the application of above graphs we have calculated the parameters like Power dissipation and Slew rate rise or fall. Here power dissipation is coming out to be negative because in the circuit we have active elements and because of them flow of charges take place from negative potential to positive potential.

TABLE 4.5: Electrical parameters of the Gaussian-Gaussian MAX Composition

| <b>Electrical Parameters</b> | Value     |

|------------------------------|-----------|

| Power Dissipation            | -2.22872n |

| Slew Rate (Rise)             | 1.73052u  |

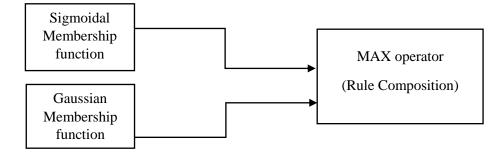

#### 2. Sigmoidal-Gaussian composition (using MAX operator)

We have passed the two membership functions Sigmoidal and Gaussian to MAX circuit as shown below in the block diagram fig. 4.15 and hence we got the output as per rule composition shown in fig. 4.16. Inputs are also shown in the same figure.

FIGURE 4.15: Block Diagram showing MAX operator rule composition using Sigmoidal & Gaussian function

We have inputs at V (D2) and V (D3). At V (D2) we are providing S-membership function as an input and at V (R46) we are providing Gaussian membership function.

Output V (R46) initially follows S membership function and then Gaussian membership function. This is how we get the following output.

**FIGURE 4.16: Output corresponding to the MAX circuit using Sigmoidal & Gaussian function** Here with the application of above graphs we have calculated the parameters like Power dissipation and Slew rate rise or fall. Here power dissipation is coming out to be negative because in the circuit we have active elements and because of them flow of charges take place from negative potential to positive potential.

TABLE 4.6:

Electrical parameters of the Sigmoidal-Gaussian MAX Composition

| Electrical Parameters | Value      |

|-----------------------|------------|

| Power Dissipation     | -32.47138u |

| Slew Rate (Rise)      | 1.92162u   |

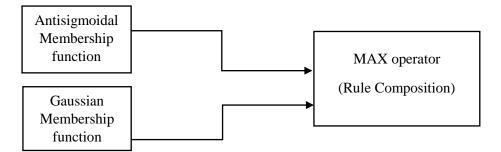

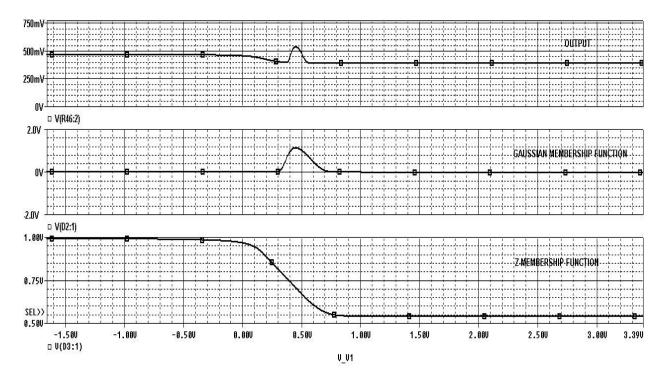

#### 3. Antisigmoidal-Gaussian composition (using MAX operator)

We have passed the two membership functions Antisigmoidal and Gaussian to MAX circuit as shown below in the block diagram fig. 4.17 and hence we got the output as per rule composition shown in fig. 4.18. Inputs are also shown in the same figure. Fig. 4.19 showing combined figure where output is highlighted.

FIGURE 4.17: Block Diagram showing MAX operator rule composition using Antisigmoidal & Gaussian function

In order to achieve the following output we fed Z-membership function at V (D3) and Gaussian membership function at V (D2) of MIN circuit. Output (R46) initially it follows the Z membership function and then it follows Gaussian membership function.

FIGURE 4.18: Output corresponding to the MAX circuit using Antisigmoidal & Gaussian function

FIGURE 4.19: Output corresponding to the MAX circuit using Antisigmoidal & Gaussian function (combined)

Here with the application of above graphs we have calculated the parameters like Power dissipation and Slew rate rise or fall. Here slew rate is positive because it is taken as slew rate rise.

TABLE 4.7:

Electrical parameters of the Antisigmoidal-Gaussian MAX Composition

| Electrical Parameter | Value     |

|----------------------|-----------|

| Power Dissipation    | -30.1235u |

| Slew Rate (Rise)     | 1.45172u  |

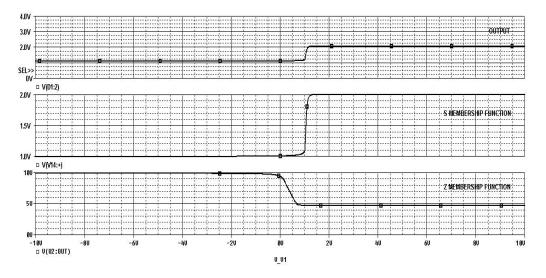

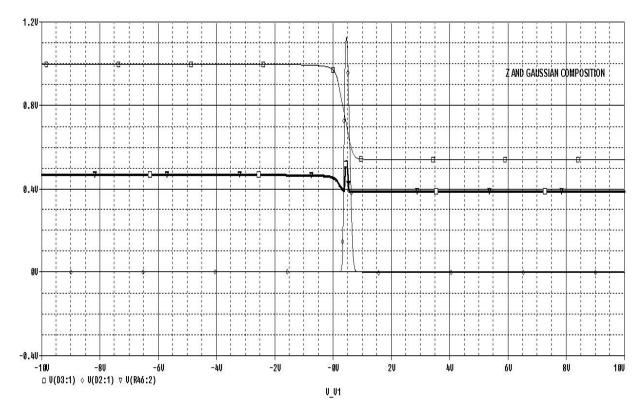

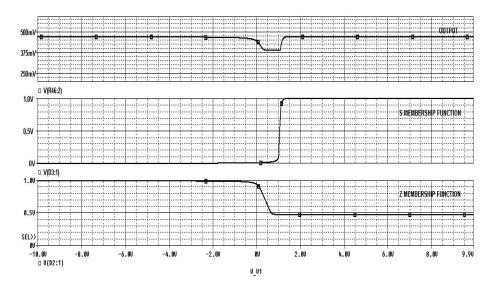

#### 4. Sigmoidal-Antisigmoidal composition (using MAX operator)

We have passed the two membership functions Antisigmoidal and Sigmoidal to MAX circuit as shown below in the block diagram fig. 4.20 and hence we got the

output as per composition shown in fig. 4.21. Inputs are also shown in the same figure.

FIGURE 4.20: Block Diagram showing MAX operator rule composition using Antisigmoidal & Sigmoidal function

Here we have provided inputs S and Z respectively at V (D3) and V(D2). S membership function has voltage range varying from 0V to 1V and Z membership function from 0.4V to 1V.

FIGURE 4.21: Output corresponding to the MAX circuit using Z & S function

Here with the application of above graphs we have calculated the parameters like Power dissipation and Slew rate rise or fall. Here power dissipation is coming out to be negative because in the circuit we have active elements and because of them flow of charges take place from negative potential to positive potential.

| <b>Electrical Parameters</b> | Value      |

|------------------------------|------------|

| Power Dissipation            | -32.52822u |

| Slew Rate (Rise)             | 2.00157u   |

TABLE 4.8:

Electrical parameters of the Sigmoidal-Antisigmoidal MAX Composition

## **CONCLUSION AND FUTURE WORK**

In this report, we had made an attempt for designing the fuzzy membership functions and its electronic implementation. We have successfully designed and implemented the Gaussian – membership function and optimized Z - membership function. We have calculated its various electrical parameters like Slew Rate and power dissipation. We have also implemented the rule composition using membership functions like Gaussian, Sigmoidal, Antisigmoidal in MIN and MAX operators and calculated their electrical parameters also.

In future, we are going to replace OP-AMP inverter circuit with the MOSFET inverter circuit in the proposed circuit by which we can also bring changes in the gain. Moreover we will also going to try to replace OP-AMP with the current amplifier in the existed circuit of S, Z, Triangular and Trapezoidal membership function. Also in future the remaining steps of Fuzzy System Model like Implication, Aggregation and Defuzzification can be implemented.

#### LIST OF PUBLICATIONS

Paras Goyal, Sachin Arora, Dalchand Sharma, Shruti Jain, "Design and Simulation of Gaussian Membership function", International Journal of Innovative Research in Electrical, Electronics. Instrumentation Control Engineering, 4(2), 26-28:2016. and pp DOI: 10.17148/IJIREEICE.2016.4208

#### http://ijireeice.com/upload/2016/february-16/IJIREEICE%208.pdf

# Design and Simulation of Gaussian Membership Function

Paras Goyal<sup>1</sup>, Sachin Arora<sup>2</sup>, Dalchand Sharma<sup>3</sup>, Shruti Jain<sup>4</sup>

Department of Electronics and Communication Engineering,

Jaypee University of Information Technology, Solan, Himachal Pradesh, India<sup>1,2,3,4</sup>

Abstract: This paper presents the proposed circuit for the designing of the Gaussian membership function using electronic devices like metal oxide semiconductor field effect transistor (MOSFET), operational amplifier (OPAMP) in ORCAD. Proposed circuit includes concepts of current mirror and current sink. In the proposed circuit we can also have S and Z membership functions by varying various voltages.

Keywords: Metal oxide Semiconductor Field Effect Transistor, Operational Amplifier, Fuzzy System, Membership Functions, Current Mirror, Current Sink,

#### I. INTRODUCTION

Fuzzy membership functions are used to determine the . The source terminals are to be connected degree to which they belong to each of the appropriate . Drain current of both the PMOS are to be equal fuzzy sets [1-4]. We always provide the crisp value as an input and the output is a fuzzy degree of membership in the qualifying linguistic variable. The proposed circuit in Current Sink is a two terminal device whose current is this paper is made using the several electronic devices like always independent of the voltage across its terminals. operational amplifier, metal oxide semiconductor field Current flows from positive node, through sink, to the effect transistor, current sink, and current mirror circuit [5- negative node. Typically negative node is at V15. Gate 7].

- $(I_{D1} = I_{D2})$

voltage is applied to create the desired value of current

#### **REFERENCES**

- 1. Gayakwad, R.A. (2002) Op-Amps and Linear Integrated Circuits, 3<sup>rd</sup> edition, Prentice Hall of India Pvt. Ltd., New Delhi.

- 2. Shruti Jain, "Design and simulation of fuzzy membership functions for the fuzzification module of fuzzy system using operational amplifier", International Journal of Systems, Control and Communications (IJSCC), 69-83, 6(1):2014.

- 3. Fuzzy Control System, http://en.Wikipedia.org/wiki/Fuzzy\_control\_system

- 4. Fuzzy Logic, http://en.Wikipedia.org/wiki/Fuzzy\_logic

- 5. Fuzzy Logic and its uses

http://www.doc.ic.ac.uk/~nd/surprise\_96/journal/vol4/sbaa/report.html

- 6. Drankov, D., Hellendoorn, H. and Reinfrank, M. (1993) An introduction to Fuzzy Control, Springer-Verlag, New York.

- 7. OP-AMP as Differential Amplifier,

http://cc.ee.ntu.edu.tw/~lhlu/eecourses/Electronics1/Electronics\_Ch2.pdf

- 8. OP-AMP, http://www.electronics-tutorials.ws/opamp\_5.html

- 9. J.F. Baldwin, "Fuzzy logic and fuzzy reasoning," in Fuzzy Reasoning and Its Applications, E.H. Mamdani and B.R. Gaines (eds.), London: Academic Press, 1981.

- 10. W. Bandler and L.J. Kohout, "Semantics of implication operators and fuzzy relational products," in Fuzzy Reasoning and Its Applications, E.H. Mamdani and B.R. Gaines (eds.), London: Academic Press, 1981.

- 11. M. Eschbach and J. Cunnyngham, "The logic of fuzzy Bayesian influence," paper presented at the International Fuzzy Systems Association Symposium of Fuzzy information Processing in Artificial Intelligence and Operational Research, Cambridge, England: 1984.

- 12. F. Esragh and E.H. Mamdani, "A general approach to linguistic approximation," in Fuzzy Reasoning and Its Applications, E.H. Mamdani and B.R. Gaines (eds.), London: Academic Press, 1981.

- Shruti Jain, "Design and Simulation of Fuzzy System Using Two Stage CMOS Operational Amplifier", Journal of Active and Passive Electronic Devices, 2014, 9(4), 329-338

- 14. J. Fox, "Towards a reconciliation of fuzzy logic and standard logic," Int. Jrnl. of Man-Mach. Stud., Vol. 15, 1981, pp. 213-220.

- 15. S. Haack, "Do we need fuzzy logic?" Int. Jrnl. of Man-Mach. Stud., Vol. 11, 1979, pp.437-445.

- 16. S. Korner, "Laws of thought," Encyclopedia of Philosophy, Vol. 4, MacMillan, NY: 1967, pp. 414-417.

- 17. C. Lejewski, "Jan Lukasiewicz," Encyclopedia of Philosophy, Vol. 5, MacMillan, NY: 1967, pp. 104-107.

- 18. T. Radecki, "An evaluation of the fuzzy set theory approach to information retrieval," in R. Trappl, N.V. Findler, and W. Horn, Progress in Cybernetics and System Research, Vol. 11: Proceedings of a Symposium Organized by the Austrian Society for Cybernetic Studies, Hemisphere Publ. Co., NY: 1982.

- 19. I.G. Umbers and P.J. King, "An analysis of human decision-making in cement kiln control and the implications for automation," Int. Jrnl. of Man-Mach. Stud., Vol. 12, 1980, pp. 11-23.

- 20. F. Wenstop, "Deductive verbal models of organizations," Int. Jrnl. of Man-Mach. Stud., Vol. 8, 1976, pp. 293-311.

- 21. L.A. Zadeh, "Fuzzy sets," Info. & Ctl., Vol. 8, 1965, pp. 338-353.

- 22. L.A. Zadeh, "Fuzzy algorithms," Info. & Ctl., Vol. 12, 1968, pp. 94-102.

- 23. L.A. Zadeh, "Making computers think like people," I.E.E.E. Spectrum, 8/1984, pp. 26-32.

- 24. MOSFETS, http://www.electronics-tutorials.ws/fet/mosfet.html